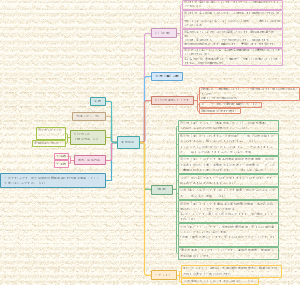

导图社区 嵌入式处理器思维导图

- 131

- 10

- 0

- 举报

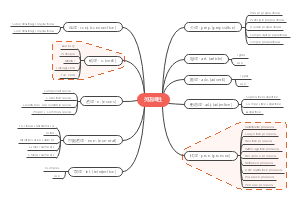

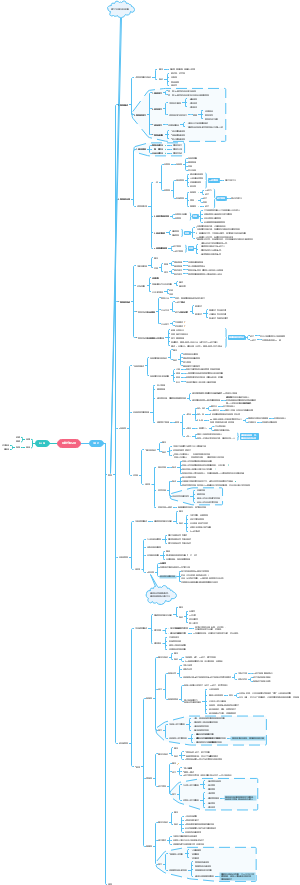

嵌入式处理器思维导图

本导图整理了计算机三级嵌入式处理器中ARM处理器的内容,主要特点、指令集、分类、体系结构、异常、ARM存储器等等。

编辑于2021-08-16 11:18:45- 存储器

- 体系结构

- 嵌入式处理器

- 相似推荐

- 大纲

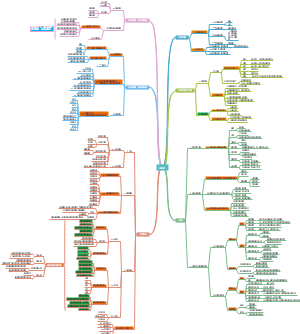

嵌入式处理器

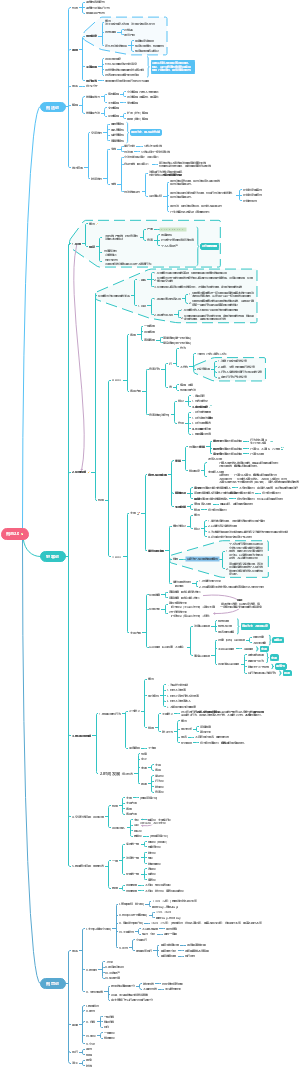

2.ARM处理器

1. 主要特点

RISC多为哈弗结构,主流为32位

单周期操作

只使用加载/存储(Load/Store)指令访问内存

指令长度固定

三地址指令格式

指令流水线技术

低功耗设计

2. 架构的发展

。。。。。。

3. 指令集

ARM 指令集

32位指令

进行8、16、32位整数运算

以字为边界对齐

通过扩展的协处理器(最多16个)可扩充

浮点运算指令

数字信号处理【DSP】

单指令多数据【SIMD】等

Thumb 指令集

16位指令

减少代码量、提高代码密度

以2字节为边界对齐

只支持通用功能

Thumb-2指令集

16、32位指令

实现代码密度和处理器性能的最佳平衡

4. 分类

淘汰

ARMv1、ARMv2、ARMv3

经典ARM处理器

主要为ARMv7、ARM9、ARM11系列

ARM9系列

ARM920T

S3C2410

S3C2440

ARM Cortex处理器

Cortex-M(CM)

性价比极高,成本低,功耗极小

适用于对成本和功耗敏感的微控制器(MCU)和终端应用

均为32位RISC处理器

只支持Thumb-2指令集

款式

应用

CM0/CM0+

成本低,简单,中低端

CM3

性能高通用性好,中高端

CM4

数字信号控制功能

CM0

市场上体积最小,能耗最低(门电路少)(16μW/MHz)的ARM处理器

基于ARMv6M架构,冯氏存储结构、3级流水线

56条Thumb-2指令

以CM0为内核的MCU,SoC

医疗器械,电子测量,智能控制等

CM0+/M1/M3/M4

CM3

低功耗、门数少、中断延迟短、调试成本低、集成度高

基于ARMv7-M架构,哈弗存储结构、3级流水线

Thumb-2指令

硬件除法指令

外围组件可选

CM4比CM3多VFP可选

Cortex-R(实时)

响应速度快,性能合理,功耗低

高性能、实时处理、安全、低成本

汽车电子、硬盘驱动控制器、手机等

Cortex-A(应用)

高端应用,频率高,性能好,功耗合理

A5~A15——32位

A53-A57——64位

ARM专家处理器

专用于智能卡安全应用领域

SC000系列

基于ARM7TDMI

SC100系列

基于Cortex-M0

SC300系列

基于Cortex-M3

5. 体系结构

工作状态

ARM状态

32位状态

Thumb-2状态

16位状态

异常处理时必须执行32位的ARM指令

调试状态

处理器停机调试时进入

工作模式(除Cortex外支持7种模式)

用户模式User

10000

快速中断模式FIQ

10001

外部中断模式IRQ

10010

管理模式SVC

10011

CPSR[M4:M0]

中止模式ABT

10111

未定义指令模式UND

11011

系统模式SYS

11111

转换

处理器处于用户模式时,发生异常,处理器改变CPSR,转换工作模式

寄存器组织

ARM状态

37个寄存器

31个32位通用寄存器(含PC)

R0~R7

8个不分组寄存器

R8~R12

共2组10个

标有fiq的表示快速中断模式专用

R13~R14

共6组12个

专门用于特定模式的寄存器

R15

作PC

6个状态寄存器

程序状态寄存器格式

条件码标志4个

N-符号标志

Z-全0标志

C-进错位标志

V-溢出标志

Q

增强的DSP运算指令是否溢出的标志

控制位8个

I-中断禁止控制位

F-禁止快速中断FIQ的控制位

T-ARM与Thumb指令切换控制位

M4~M0-模式选择位

Thumb状态

。。。。。。

内置MMU的ARM处理器中的寄存器

CP15

C0~C15共16个

6. 异常

简述

每执行一条ARM指令PC值加4,每执行一条Thumb指令PC值加2

是由于内部事件或外部事件引起的请求,使处理器去做相应处理的事件

经典ARM异常种类及32位的向量地址(优先级1~6)

1.复位RESET

0x00000000

2.数据访问中止DABT

0x00000010

3.快速中断请求FIQ

0x0000001C

4.外部中断请求IRQ

0x00000018

5.指令预取中止PABT

0x0000000C

6.未定义的指令UND

0x00000004

6.软件中断SWI

0x00000008

互斥(不可能同时发生)

ARM异常的中断响应过程

。。。。。。

从异常处理程序中返回

。。。。。。

7. ARM存储器

简述

是从0x00000000地址开始的以字节为单位的线性阵列

每个数据字32位占4字节的地址空间

存储字的格式

大端模式

32位数据字的高字节存储在低地址中,而低字节存放在高地址中

小端模式

32位数据字的高字节存放在高地址,低字节放在低地址

系统复位时一般自动默认为小端,与Intel 80x86一致

数据类型

32位ARM处理器(除C-A50外)

字节(8位)

半字(16位)

2字节对齐(地址的最低位为0)

字(32位)

4字节对齐(地址的低两位为0)

每种又支持有(无)符号数,故共6种

8. ARM处理器中的

存储器管理单元【MMU】

许多高性能处理器重要部件

虚拟存储技术

功能

虚拟地址到物理地址的转换

存储器访问权限控制

存储器访问的顺序

。。。。。。

存储器保护单元【MPU】

使用不同的域来管理和控制指令内存和数据内存

9. ARM处理器指令集

10. ARM汇编语言程序设计

1.概述

结构类型

分类

指令集

内容

基本数据类型、寄存器、寻址模式、指令、中断、异常处理一级外部I/O等

称为 指令集体系结构/IS架构【ISA】

分类

复杂指令集结构【CISC】

指令集中,指令数目多,结构比较复杂,包含专用指令,长度不等,功耗大

Intel x86 处理器(广泛使用在个人计算机),CDC 6600,System/360,VAX等

精简指令集结构【RISC】

指令数目较少,指令字长统一,格式规整,操作简单,执行时间短

ARC、ARM、AVR、MIPS、PA-RISC、SPARC、PowerPC等

存储机制

冯·诺依曼结构

哈弗结构

多层次的存储器结构

在处理器与主存储器之间加缓冲器【Cache存储器】

x86系列、高端ARM

字长

8、16、32、64位结构

内核系类

51、ACR、PIC、PowerPC、ARM等

简介

。。。。。。

ARM处理器

1. 主要特点

RISC多为哈弗结构,主流为32位

单周期操作

只使用加载/存储(Load/Store)指令访问内存

指令长度固定

三地址指令格式

指令流水线技术

低功耗设计

2. 架构的发展

。。。。。。

3. 指令集

ARM 指令集

32位指令

进行8、16、32位整数运算

以字为边界对齐

通过扩展的协处理器(最多16个)可扩充

浮点运算指令

数字信号处理【DSP】

单指令多数据【SIMD】等

Thumb 指令集

16位指令

减少代码量、提高代码密度

以2字节为边界对齐

只支持通用功能

Thumb-2指令集

16、32位指令

实现代码密度和处理器性能的最佳平衡

4. 分类

淘汰

ARMv1、ARMv2、ARMv3

经典ARM处理器

主要为ARMv7、ARM9、ARM11系列

ARM9系列

ARM920T

S3C2410

S3C2440

ARM Cortex处理器

Cortex-M(CM)

性价比极高,成本低,功耗极小

适用于对成本和功耗敏感的微控制器(MCU)和终端应用

均为32位RISC处理器

只支持Thumb-2指令集

款式

应用

CM0/CM0+

成本低,简单,中低端

CM3

性能高通用性好,中高端

CM4

数字信号控制功能

CM0

市场上体积最小,能耗最低(门电路少)(16μW/MHz)的ARM处理器

基于ARMv6M架构,冯氏存储结构、3级流水线

56条Thumb-2指令

以CM0为内核的MCU,SoC

医疗器械,电子测量,智能控制等

CM0+/M1/M3/M4

CM3

低功耗、门数少、中断延迟短、调试成本低、集成度高

基于ARMv7-M架构,哈弗存储结构、3级流水线

Thumb-2指令

硬件除法指令

外围组件可选

CM4比CM3多VFP可选

Cortex-R(实时)

响应速度快,性能合理,功耗低

高性能、实时处理、安全、低成本

汽车电子、硬盘驱动控制器、手机等

Cortex-A(应用)

高端应用,频率高,性能好,功耗合理

A5~A15——32位

A53-A57——64位

ARM专家处理器

专用于智能卡安全应用领域

SC000系列

基于ARM7TDMI

SC100系列

基于Cortex-M0

SC300系列

基于Cortex-M3

5. 体系结构

工作状态

ARM状态

32位状态

Thumb-2状态

16位状态

异常处理时必须执行32位的ARM指令

调试状态

处理器停机调试时进入

工作模式(除Cortex外支持7种模式)

用户模式User

10000

快速中断模式FIQ

10001

外部中断模式IRQ

10010

管理模式SVC

10011

CPSR[M4:M0]

中止模式ABT

10111

未定义指令模式UND

11011

系统模式SYS

11111

转换

处理器处于用户模式时,发生异常,处理器改变CPSR,转换工作模式

寄存器组织

ARM状态

37个寄存器

31个32位通用寄存器(含PC)

R0~R7

8个不分组寄存器

R8~R12

共2组10个

标有fiq的表示快速中断模式专用

R13~R14

共6组12个

专门用于特定模式的寄存器

R15

作PC

6个状态寄存器

程序状态寄存器格式

条件码标志4个

N-符号标志

Z-全0标志

C-进错位标志

V-溢出标志

Q

增强的DSP运算指令是否溢出的标志

控制位8个

I-中断禁止控制位

F-禁止快速中断FIQ的控制位

T-ARM与Thumb指令切换控制位

M4~M0-模式选择位

Thumb状态

。。。。。。

内置MMU的ARM处理器中的寄存器

CP15

C0~C15共16个

6. 异常

简述

每执行一条ARM指令PC值加4,每执行一条Thumb指令PC值加2

是由于内部事件或外部事件引起的请求,使处理器去做相应处理的事件

经典ARM异常种类及32位的向量地址(优先级1~6)

1.复位RESET

0x00000000

2.数据访问中止DABT

0x00000010

3.快速中断请求FIQ

0x0000001C

4.外部中断请求IRQ

0x00000018

5.指令预取中止PABT

0x0000000C

6.未定义的指令UND

0x00000004

6.软件中断SWI

0x00000008

互斥(不可能同时发生)

ARM异常的中断响应过程

。。。。。。

从异常处理程序中返回

。。。。。。

7. ARM存储器

简述

是从0x00000000地址开始的以字节为单位的线性阵列

每个数据字32位占4字节的地址空间

存储字的格式

大端模式

32位数据字的高字节存储在低地址中,而低字节存放在高地址中

小端模式

32位数据字的高字节存放在高地址,低字节放在低地址

系统复位时一般自动默认为小端,与Intel 80x86一致

数据类型

32位ARM处理器(除C-A50外)

字节(8位)

半字(16位)

2字节对齐(地址的最低位为0)

字(32位)

4字节对齐(地址的低两位为0)

每种又支持有(无)符号数,故共6种

8. ARM处理器中的

存储器管理单元【MMU】

许多高性能处理器重要部件

虚拟存储技术

功能

虚拟地址到物理地址的转换

存储器访问权限控制

存储器访问的顺序

。。。。。。

存储器保护单元【MPU】

使用不同的域来管理和控制指令内存和数据内存

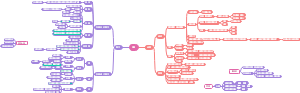

9. ARM处理器指令集

10. ARM汇编语言程序设计