导图社区 CVD

- 112

- 3

- 1

- 举报

CVD

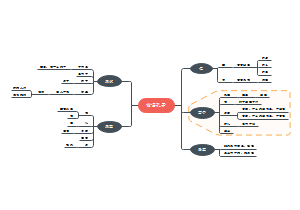

CVD思维导图:包含Def:是把构成薄膜元素的气态反应剂或液态反应剂的蒸气以合理的流速引入反应室,在衬底表面发生化学反应并在衬底上淀积薄膜的工艺方法等等

编辑于2022-04-14 09:33:18- 微电子工艺

- 化学气相…

- CVD

- Cha5 CMOS放大器

集成电路(integrated circuit)是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;

- 模拟COMS子电路

CMOS逻辑电路代表互补的金属氧化物半导体(Complementary Metal-Oxide-Semiconductor),它指的是一种特殊类型的电子集成电路(IC)。

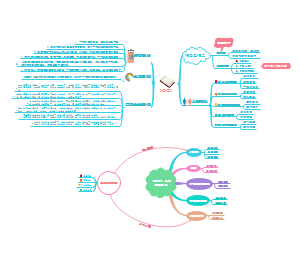

- 自控力

这是一篇关于自控力的思维导图,当我们将意志力挑战看成是衡量道德水平的标准时,善行就会允许我们做坏事。为了更好地自控,我们需要忘掉美德,关注目标与价值。

CVD

社区模板帮助中心,点此进入>>

- Cha5 CMOS放大器

集成电路(integrated circuit)是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;

- 模拟COMS子电路

CMOS逻辑电路代表互补的金属氧化物半导体(Complementary Metal-Oxide-Semiconductor),它指的是一种特殊类型的电子集成电路(IC)。

- 自控力

这是一篇关于自控力的思维导图,当我们将意志力挑战看成是衡量道德水平的标准时,善行就会允许我们做坏事。为了更好地自控,我们需要忘掉美德,关注目标与价值。

- 相似推荐

- 大纲

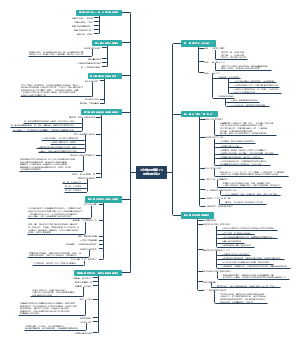

CVD

Def:是把构成薄膜元素的气态反应剂或液态反应剂的蒸气以合理的流速引入反应室,在衬底表面发生化学反应并在衬底上淀积薄膜的工艺方法。

分类:常压化学气相淀积APCVD 低压化学气相淀积LPCVD, 等离子增强化学气相淀积PECVD, 金属有机物化学气相淀积MOCVD, 激光诱导化学气相淀积LCVD 微波等离子体化学气相淀积MWCVD

工艺原理

薄膜淀积

反应方程式:SiH4(吸附)=Si+2H2(气)(总)

反应步骤:(1)反应剂气体(或被惰性气体稀释的反应剂)以合理的流速被输送到反应室内,气流从入口进入反应室并以平流形式向出口流动,平流区也称为主气流区,其气体流速是不变的,如上图所示。 (2)反应剂从主气流区以扩散方式通过边界层到达衬底表面,边界层是主气流区与硅片表面之间气流速度受到扰动的气体薄层。 (3)反应剂被吸附在硅片的表面,成为吸附原子(分子)。(4)吸附原子(分子)在衬底表面发生化学反应,生成薄膜的基本元素并淀积成薄膜。 (5)化学反应的气态副产物和未反应的反应剂离开衬底表面,进入主气流区被排出系统。

淀积过程

反应条件:(1)在淀积温度下,反应剂需有足够高的蒸气压; (2)除淀积物外,反应的其它物质必须是挥发性; (3)淀积物本身必须具有足够低的蒸气压; (4)薄膜淀积所用的时间必须足够短---高效率, 低成本; (5)淀积温度必须足够低--避免对先前工艺影响; (6)CVD不允许化学反应的气态副产物进入薄膜; (7)化学反应必须在被加热的衬底表面进行。

淀积影响因素

温度

在低温条件下.薄膜淀积速率与温度之间遵循着指数关系。随着温度的上升,淀积速率也随之加快. 当温度高过某个值之后.淀积速率趋向于稳定

反应剂浓度

增加气流速率可以提高淀积速率。但如果气流速率持续上升,薄膜淀积速率最终会达到一个极大值,之后与气流速率无关。这是因为气流速率大到一定程度时,淀积速率转受表面化学反应速率控制

质量的控制

覆盖特性

保形覆盖:无论衬底表面有什么样的倾斜图形,在所有图形上面都能淀积有相同厚度的薄膜。 与之对应的即非保型覆盖。

在质量输运控制的淀积过程,衬底表面上任何一点所淀积的薄膜厚度取决于到达该点的反应剂数量----由工艺过程压力和吸附原子的迁移性决定。

吸附原子的迁移率与吸附原子的种类、能量、衬底温度、离子对吸附原子的轰击有关: 高温,LPCVD----高保形性 低温,APCVD----非保形性

到达角

指反应剂能够从各方向到达表面的某一点,这全部方向角就是改点的到达角

到达角越大到达该点的反应剂分子数量就越多,该点薄膜越厚。

遮蔽(Shadowing)效应-衬底表面上的图形对反应剂气体分子直线运动的遮挡作用。 既是对入射离子的一种阻挡作用,其会影响覆盖的保型性。

三种机制影响反应气体分子到衬底表面的特殊位置:入射;再发射;表面迁移 再发射机制是决定保形覆盖的关键因素 TEOS粘滞系数比硅烷小,再发射率高,保形覆盖更好。

薄膜内应力

拉应力 (tensile stress)

压应力 (compressive stress)

薄膜的致密性:主要由淀积过程中衬底温度决定,温度越高淀积原子在表面迁移、排列速度越快,致密性就越好,产生的气态副产物从表面解析、被排出的越快。 温度过高超出工艺范围,使表面吸附的反应剂还来不及反应就会解析离开衬底,难以淀积成膜,即使成膜也会有质量(表面粗糙、平整度差)问题。 对致密性差的薄膜可以通过高温退火提高其致密度 淀积速率越快致密性越差。

厚度均匀性:主要由薄膜淀积速率的均匀性决定,而淀积速率主要由温度和反应剂浓度决定。如果反应室出现温度不均匀或者反应剂浓度不均匀,就会使得同一衬底不同位置,或者不同衬底之间出现厚度不均匀。

薄膜的附着性:一般来说CVD工艺淀积的薄膜,与衬底的附着性都很好,因为CVD工艺淀积薄膜是通过化学反应在衬底表面生成的,自身能量较高,反应剂分子(或原则)与衬底分子会形成化学键来降低系统自由能,所以薄膜与衬底之间的结合牢固。 工艺过程中温度越高,薄膜和衬底结合的就越牢靠。

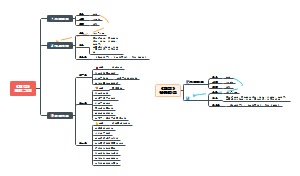

工艺方法

设备

CVD系统通常包含如下子系统: ① 气态源或液态源; ② 气体输入管道; ③ 气体流量控制系统; ④ 反应室; ⑤ 基座加热及控制系统(有些系统的反应激活能通过其他方法引入); ⑥ 温度控制及测量系统等。 LPCVD和PECVD系统还包含减压系统。

气体源

①冒泡法; ②加热液态源; ③液态源直接注入法。

CVD过程中,可以用气态源也可以用液态源。 目前气态源正在被液态源所取代: 相对于有毒、易燃、腐蚀性强的气体,液态源会更安全一些;液体的气压比气体的气压要小的多,因此在泄漏事故当中,液体产生致命的危险比较小; 除了安全考虑之外,许多薄膜采用液体源淀积时有较好的特性。

常压化学气相淀积 (APCVD)

优点:操作简单,淀积速率较高(>0.1mm/min),适于介质薄膜的淀积。

缺点:易于发生气相反应、产生微粒污染,台阶覆盖性和均匀性比较差。

其他特点:APCVD由质量输运控制淀积速率,可精确控制在单位时间内到达每个硅片表面及同一表面不同位置的反应剂数量----薄膜均匀性。

反应器

水平式反应器

垂直反应器

桶型反应器

低压化学气相淀积 (LPCVD)

优点

低压可以大大提高hg的值。 增加产率 — 晶片可直插放置许多片(100-200) 工艺对温度灵敏,但是采用温度控制好的热壁式系统可解决温度控制问题 气流耗尽仍是影响均匀性的因素,可以设定温差5~25 C,或分段进气

缺点

气缺现象:LPCVD系统中,只有一个入气口的反应室来说,沿气流方向因反应剂不断消耗,靠近入气口处淀积的膜较厚,远离入气口处淀积的膜较薄。

减轻气缺现象的方法: 1)可通过在水平方向上逐渐提高温度来加快反应速度,从而提高淀积速率,补偿气缺效应的影响,减小各处淀积厚度的差别。 2)采用分布式的气体入口 3)增加反应室中的气流速度

相对低的淀积速率和相对高的工作温度。增加反应剂分压来提高淀积速率则容易产生气相反应;降低淀积温度则将导致不可接受的淀积速率。

等离子增强化学气相淀积 (PECVD)

采用射频等离子体把电能耦合到气体中,促进化学反应在较低温度下进行。

优点

低温淀积,可以在铝上淀积二氧化硅或者氮化硅。淀积的薄膜具有良好的附着性、低针孔密度、良好的阶梯覆盖及电学特性。

射频功率使反应器中低压气体非平衡辉光放电。衬底吸附等离子体内活泼的中性原子团与游离基,在表面发生化学反应生成薄膜物质,并不断受到离子和电子轰击,容易迁移、重排,使得淀积薄膜均匀性好,填充小尺寸结构能力强。

影响因素

反应器的结构

射频功率的强度和频率

反应剂与稀释剂气体量

抽气速率

衬底温度

CVD工艺方法的进展

高密度等离子体化学气相淀积

热丝化学气相淀积

激光诱导化学气相淀积

金属有机物化学气相淀积

等离子体的产生

直流气体辉光放电

无光放电区:极少量原子受到高能宇宙射线激发而电离;电流微弱、,且不稳定

汤生放电区:电压升高,电子、离子的能量逐渐升高,α作用;γ作用;

辉光放电:气体放电击穿;负阻现象;阴极电流密度一定,有效放电面积随电流增加而增大;

反常辉光放电:阴极全部成为有效放电区域,只有增加功率才可增加阴极电流密度

电弧放电:随电流增加,放电电压再次大幅下降

等离子体及其特点

Def:等离子体(Plasma)是指具有一定导电能力的气体,它由正离子、电子、光子以及原子、原子团、分子及它们的激发态所组成的混合气体,宏观上呈现电中性。

等离子体中高速运动的电子与其它粒子的碰撞是维持气体放电的主要微观机制。

辉光放电构成的等离子体中粒子能量、密度较低,放电电压较高。其特点是质量较大的重粒子,包括离子、中性原子和原子团的能量远远低于电子的能量,是一种非热平衡状态的等离子体。

弹性碰撞:无激发、电离或复合 非弹性碰撞:动能转变为内能 维持了自持放电

射频气体辉光放电

在一定气压条件下,在阴阳电极之间加交变电压频率在射频范围时,会产生稳定的射频辉光放电。

激发源

E型放电:高频电场直接激发

H型放电:高频磁场感应激发

与直流放电的不同

电场周期性改变方向,带电粒子不容易到达电极和器壁,减少了带电粒子的损失。在两极之间不断振荡运动的电子可从高频电场中获得足够能量,使气体分子电离,电场较低就可维持放电。

阴极产生的二次电子发射不再是气体击穿必要条件

射频电场可由容抗或感抗耦合进淀积室。电极可以是导体,也可是绝缘体。

高密度等离子体的产生

Def:指其离子浓度超过1011ions/cm3

产生:一般都是在简单等离子体发生器上增设电场和磁场,用横向电场和磁场来增加电子在等离子体中的行程,从而使电子和原子(或分子)之间碰撞更加频繁,以增加等离子体中的离子和活性基团。

产生方法

电感耦合HDP

磁控HDP

电子回旋共振(ECR)HDP技术

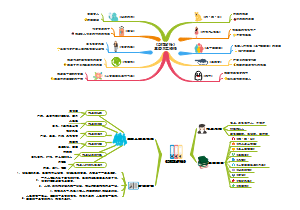

氮化硅薄膜

作为掩蔽膜

非晶介质薄膜,Si3N4薄膜一般是采用CVD法制备,在二氧化硅不适合的场合作为介质薄膜使用。

无定形的绝缘材料,在集成电路中可以作为钝化层和选择性氧化的掩蔽膜。

LPCVD氮化硅的反应式:

影响因素:温度、总气压、反应剂比例、反应室内的温度梯度。

作为钝化层

原因: (1) 具有非常强的掩蔽能力,尤其是钠和水汽在氮化硅中扩散速度非常慢; (2) 通过PECVD可以制备出具有较低压应力的氮化硅薄膜; (3) 可以对底层金属实现保形覆盖; (4) 薄膜中的针孔很少。

当用作最终的钝化层时,为了与低熔点的金属(如Al)兼容,氮化硅的淀积必须在低温下进行,首选淀积方法是PECVD。反应剂为硅烷和氨、或者为硅烷和氮,反应温度在200-400℃之间。

反应方程式:

优点

1)抗钠能力强,硬度大,针孔少,致密,化学稳定性好,因此,作为钝化膜、保护膜有优势。 2)掩蔽能力强,SiO2对B、P、As、Sb有掩蔽作用,Si3N4还可以掩蔽Ga、In、ZnO。能作为多种杂质的掩蔽膜。 3)介电常数ε大、导热性好,εSiO2 4.2,εSi3N4 6-9,可做电容的介质层;

与二氧化硅比较

工艺用途:可以作为选择性氧化的掩膜,如MOS器件的场区氧化(LOCOS);浅沟隔离的化学机械抛光(CMP)自停止层。 问题:与硅失配率大,无论是晶格常数还是热膨胀系数,因此在Si3N4/Si界面硅缺陷大,成为载流子陷阱,或者复合中心,影响硅的载流子迁移率。

工艺

LPCVD

薄膜密度高(2.9~3.1g/cm3);介电常数6;化学配比较好;耐HF腐蚀;H含量较PECVD氮化硅低;台阶覆盖性较好;较少的粒子污染 缺点是薄膜应力较大,易破裂 LPCVD以SiH2Cl2或SiCl4为硅源淀积Si3N4 注意 工艺过程中NH3要充足

PECVD

若采用N2和SiH4作为反应剂,注意比例; 淀积速率低,台阶覆盖差,击穿电压低; H含量较少,形成薄膜致密; NH3更易于在PECVD反应室内分解,形成的薄膜性能较好

多晶硅(Poly-Si)薄膜

结构与特性

多晶硅薄膜是由无数微小单晶粒(约100nm)组成的薄膜,晶粒大小与制备工艺有关,在晶粒与晶粒之间是晶粒间界(称晶界,0.5-1nm宽),晶界原子排列无序,多晶硅薄膜呈各向同性。 晶界含大量悬挂键及高密度缺陷----晶粒间界不完整性及晶粒表面原子周期性排列受到破坏所引起。 造成多晶硅的两个重要特性: (1)扩散系数----晶界处明显大于晶粒内部 (2)杂质分凝----高温时位于晶粒内部的杂质在低温时运动到晶界处,而高温时又返回晶粒内 多晶硅内每个单晶晶粒内的电学行为和单晶硅的电学行为相似 在一般掺杂浓度下,同样掺杂情况,比单晶电阻率高; 高掺杂时,电阻率与单晶接近。

用途

MOS器件的栅电极; 超大规模集成电路中电极的多层布线; 在双极以及BiCMOS技术中,高掺杂的多晶硅薄膜也用来制作发射极; MEMS(Micro-Electro-Mechanical Systems )器件,如压力传感器的应变电阻。

物理结构特性

由小单晶的晶粒组成,存在大量的晶粒间界,晶粒内部的性质非常相似于单晶硅,晶粒间界是一个具有高密度缺陷和悬挂键的区域,这是因为晶粒间界的不完整性和晶粒表面原子周期性排列受到破坏所引起的。

在晶粒间界处的扩散系数明显高于晶粒内部的扩散系数,杂质沿晶粒间界的扩散速度比在晶粒内部的扩散速度要快得多。即使晶粒间界只占多晶硅空间的一小部分,但沿着这些途径的扩散也会使得整个多晶硅的杂质扩散速度明显增加。 杂质的分布也受到晶粒间界的影响,高温时存在于晶粒内的杂质,在低温时由于分凝作用,一些杂质会从晶粒内部运动到晶粒间界,而在高温下又会返回到晶粒内部。

电学特性

在一般的掺杂浓度下,同样的掺杂浓度,多晶硅的电阻率比单晶硅的电阻率高得多。

工艺

热分解硅烷实现淀积 SiH2(吸附)+H2(g) = Si(s)+H2(g) ↑

注意:(1)防止SiH4气相分解----应用稀释气体H2 (2)气缺现象----从反应室的入口到出口的30℃温度梯度;分布式入口LPCVD反应室 在淀积Poly-Si的同时可原位掺杂,或在淀积之后采用扩散或离子注入掺杂。

影响因素

温度; 气体压力; 反应器形状

掺杂

扩散掺杂----温度900~1000℃ N型掺杂剂:POCl5, PH3等含磷气体

优势:1.在多晶硅膜中掺入杂质浓度很高,可以超过固溶度----可得较低电阻率;2.一步完成掺杂和退火两个工艺;

缺点:工艺温度高,薄膜表面粗糙度增加

离子注入

优点:杂质数量精确可控,也可适用低掺杂薄膜制备。 电阻率为扩散掺杂法制备薄膜10倍 合适的注入能量可使杂质浓度峰值处于薄膜中间;用快速热退火(RTP) 在1150℃下不到30秒完成杂质再分布和激活。

原位掺杂

一步完成薄膜淀积和掺杂工艺;方法简单,未广泛应用

二氧化硅薄膜的淀积

用途:多层布线中金属层之间的绝缘层;MOS晶体管的栅极介质层;吸杂剂、扩散源、扩散和离子注入工艺中的掩膜;防止杂质外扩的覆盖层以及钝化层。

对SiO2膜要求

厚度均匀,结构性能好

粒子和化学沾污低

与衬底良好的黏附性

较好的台阶覆盖性,针孔密度低,产量高

完整性好以具备较高介质击穿电压

K值低

CVD SiO2特性:低温淀积SiO2薄膜的密度低于热生长SiO2,其折射系数n约为1.44(热氧化n=1.46)。 n>1.46,薄膜富硅 n<1.46, 为低密度多孔薄膜

类型

PSG

SiO2中掺磷或掺硼,目的是通过回流使芯片台阶降低,实现平整化。 向SiO2淀积源中加入硼酸三甲酯(TMB),可实现硼掺杂,加入磷酸三甲酯(TMP),可实现磷掺杂。 4PH3(g)+5O2(g) → P2O5(s)+6H2(g)

特点:应力小,阶梯覆盖较好;可吸附碱性离子; 高温下可流动

BPSG

BPSG流动性取决于薄膜的组分、工艺温度、时间与环境气氛 防止起泡现象(blistering)---- 800℃致密化; 900~975℃快速热退火 可用作绝缘层、钝化层,表面平坦化 在接触回流中,BPSG比PSG更适合

方法

APCVD /LPCVD SiO2

硅烷为源,工艺温度250-450℃,可在APCVD, LPCVD, PECVD系统中淀积。 SH4(g)+O2(g) → SiO2(s)+2H2(g) N2稀释SH4与过量O2的混合气体 低温淀积SiO2膜可在700-1000℃退火致密化,使SiO2膜的密度从2.1g/cm3增至2.2g/cm3,在HF溶液中的腐蚀速率也会降低。

TEOS (正硅酸四乙酯)为源的低温PECVD

TEOS(l){Si(OC2H5)4}+O2 → SiO2+副产物

特点:良好的台阶覆盖性,间隙填充特性,多用来形成多层布线金属层之间绝缘层淀积

中温CVD SiO2

工艺温度650-750 ℃,采用APCVD,LPCVD方法淀积。 TEOS 淀积的SiO2薄膜有更好的保形性;淀积温度: 680-730℃, 速率约25nm/min LPCVD SiO2 薄膜Si(OC2H5)4SiO2+4C2H4+2H2O

PECVD SiO2

SH4(g)+2N2O(g) → SiO2(s)+2N2(g) +2H2(g) Ar气为稀释气体,温度:200-400℃