导图社区 第五章硅外延生长

- 170

- 4

- 0

- 举报

第五章硅外延生长

硅基器件或电路制作在外延层上,器件和衬底直接产生电连接,高低压单元之间、有源层和衬底层之间的隔离通过反偏pn结完成; 而SOI电路的有源层、衬底、高低压单元之间都通过绝缘层完全隔开,各部分的电气连接被完全消除。

编辑于2022-06-29 11:02:36- 半导体材料

- 硅外延生长

- Cha5 CMOS放大器

集成电路(integrated circuit)是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;

- 模拟COMS子电路

CMOS逻辑电路代表互补的金属氧化物半导体(Complementary Metal-Oxide-Semiconductor),它指的是一种特殊类型的电子集成电路(IC)。

- 自控力

这是一篇关于自控力的思维导图,当我们将意志力挑战看成是衡量道德水平的标准时,善行就会允许我们做坏事。为了更好地自控,我们需要忘掉美德,关注目标与价值。

第五章硅外延生长

社区模板帮助中心,点此进入>>

- Cha5 CMOS放大器

集成电路(integrated circuit)是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;

- 模拟COMS子电路

CMOS逻辑电路代表互补的金属氧化物半导体(Complementary Metal-Oxide-Semiconductor),它指的是一种特殊类型的电子集成电路(IC)。

- 自控力

这是一篇关于自控力的思维导图,当我们将意志力挑战看成是衡量道德水平的标准时,善行就会允许我们做坏事。为了更好地自控,我们需要忘掉美德,关注目标与价值。

- 相似推荐

- 大纲

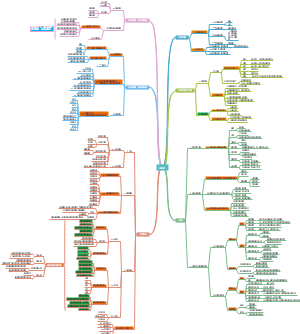

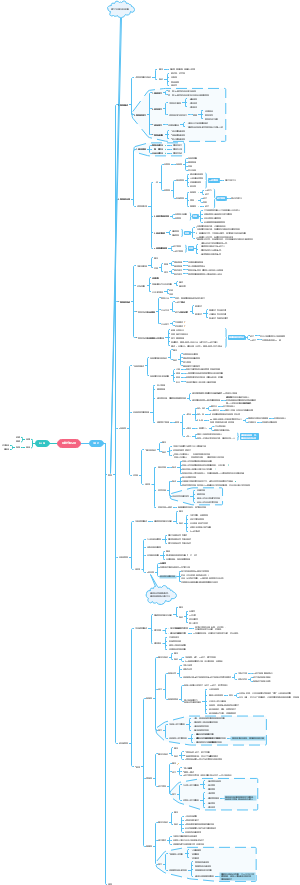

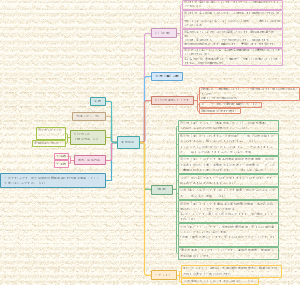

第五章 硅外延生长

概述

Def:在一定条件下,在经过切、磨、抛等仔细加工的单晶衬底上,生长一层合乎要求的单晶层的方法。生长的这层单晶叫外延层。p87

分类p87

根据外延层性质

同质外延

异质外延

根据外延生长方法

直接外延

间接外延

CVD:目前硅外延生长的主要方法

根据相变过程

真空外延

气相外延

液相外延

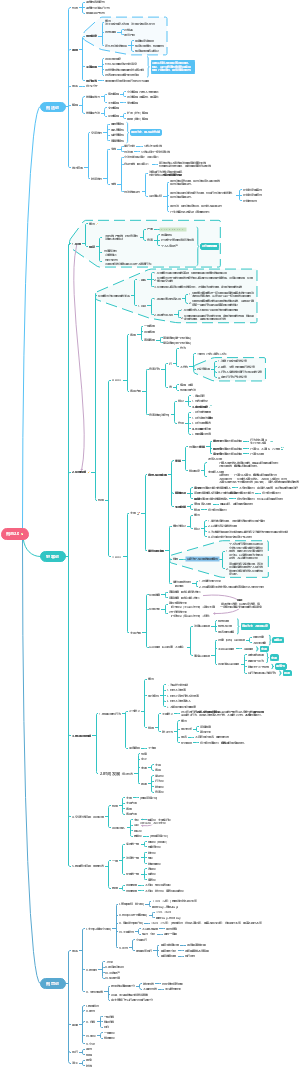

气相外延生长

原料p93

常用硅源:SiH4、SiH2Cl2、SiHCl3、SiCl4.

硅源的优缺点

SiHCl3、SiCl4 常温下为液体,外延生长温度高,但生长速度快、易纯制、使用安全、是较通用的硅源。

SiH2Cl2、SiH4 常温下为气体, SiH2Cl2使用方便,反应温度低,应用越来越广;SiH4反应温度低,无腐蚀性气体,但是会因漏气产生外延缺陷,且在高温高浓度下易发生反应生成硅粉使外延无法进行.

反应类型

氢气还原法

直接热分解法

影响p95~98

浓度

随着浓度增加,生长速率先增大后减小.

温度

温度较低时,生长速率随温度升高呈指数规律上升; 温度较高时,生长速率随温度变化较平缓;

气流速度

反应物浓度和生长温度一定时,水平式反应器中的生长速率基本上与总氢气流速的平方根成正比; 对于立式反应器,流速较低时也呈平方根关系,但流速超过一定值后,生长速率达到稳定的极限值而不再增加.

衬底晶向

生长速率<100>大于<110>大于 <111>

硅外延生长动力学过程p98

气-固表面复相化学反应模型

边界层概念

接近基座表面的流体中出现一个流体速度受到干扰而变化的薄层,而在薄层外的流速不受影响,称此薄层为边界层,也叫附面层、停滞层、滞流层; 边界层厚度与流速平方根成反比.

气相均质反应模型

外延生长反应不是在固-气界面上发生,而是在距衬底表面几微米的空间中发生.反应生成的原子或原子团再转移到衬底表面上完成晶体生长.

电阻率的控制

外延生长的掺杂p104

一般采用PCl3、AsCl3、SbCl3、AsH3做n型掺杂剂; 用BCl3、BBr3、B2H6做p型掺杂剂;

杂质的再分布p105

由于是在高温下进行外延生长,衬底中的杂质会进入外延层,使得外延层和衬底交界处的杂质浓度变平。

自掺杂p105

自掺杂效应:衬底中的杂质进入气相中再掺入外延层

基本模型

1、衬底中杂质在外延前进入到气相中,外延生长时进入生长层,主要来自背面;

2、卤化物硅源腐蚀硅片,将硅片中杂质带入外延层;

3、基座、反应室、气流系统等也会带入污染形成自掺杂。

影响:会使外延层电阻率控制受到干扰,界面处杂质分布变缓,造成器件特性偏离.

抑制自掺杂的途径

一:减少杂质由衬底逸出

使用蒸发速度较小的杂质

.外延生长前高温加热衬底

采用背面封闭技术

4. 采用低温外延技术和不含有卤原子的硅源.

采用二段外延生长技术

二:采用减压生长技术

外延层的夹层p108

指的是外延层和衬底界面附近出现的高阻层或反型层。

两种类型

在检测时导电类型混乱,击穿图形异常,用染色法观察界面不清晰.

导电类型异常,染色观察会看到一条清晰的带.

产生的原因

p型杂质沾污,造成n型外延层被高度补偿.

解决办法:p型杂质主要来源于SiCl4,只要提高SiCl4的纯度及做好外延前的清洁处理就可以解决.

由于衬底引起 衬底中基硼的含量大于31016cm-3时,外延层中就容易出现夹层

解决办法:一是提高重掺杂单晶质量;二是在工艺中防止引入p型杂质,降低单晶中的B含量;三是在外延生长时可以先长一层n型低阻层作为过渡层,控制夹层.

硅外延层的缺陷

缺陷的分类

表面缺陷,也叫宏观缺陷p109~110

云雾状表面:外延片表面呈乳白色条纹,在光亮处肉眼可以看到。一般由于氢气纯度低,含水过多,或气相抛光浓度过大,生长温度太低等引起的.

云雾状表面缺陷 ①雾圈 ②白雾 ③残迹 ④花雾

划道:由机械损伤引起

亮点:外形为乌黑发亮的小圆点

塌边:又叫取向平面,它是外延生长后在片子边缘部分比中间部分低形成的一圈或一部分宽1-2mm左右的斜平面; 形成原因:衬底加工时造成片边磨损偏离衬底片晶向.

角锥

滑移线等

内部结构缺陷,也叫微观缺陷p110~113

层错

形貌分为单线、开口、正三角形、套叠三角形和其他组态.

位错.

主要是由于原衬底位错延伸引入

另外可能是由于掺杂和异质外延时,由于不同原子半径间的差异或两种材料晶格参数差异引入内应力.

消除应力: 应力补偿法,即在外延或扩散时,同时引入两种杂质,使它们产生的应变恰好相反.当两种杂质原子掺入的比例适当时,可以使应力相互得到补偿,减少或避免晶格畸变,从而消除失配位错的产生.这种方法称为“双掺杂技术”.

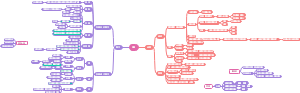

硅的异质外延

SOS外延生长 Silicon on Sapphire Silicon on Spinel p113~115

蓝宝石和尖晶石是良好的绝缘体,以它们作为衬底外延生长硅制作集成电路,可以消除集成电路元器件之间的相互作用,不但可以减少漏电流和寄生电容,增强抗辐射能力和降低功耗,还可以提高集成度和双层布线,是大规模、超大规模集成电路的理想材料.

衬底的选择

考虑外延层和衬底材料之间的相容性

包括晶体结构、熔点、蒸汽压、热膨胀系数等.

考虑衬底对外延层的沾污问题

目前最适合硅外延的异质衬底是蓝宝石和尖晶石. 当前工业生产上广泛使用蓝宝石做衬底

存在问题:自掺杂效应

solution:可采用双速率生长和两步外延等外延生长方法.

缺点

1)由于存在晶格失配(尖晶石为立方结构,蓝宝石为六角晶系)问题和自掺杂效应,外延层缺陷较多,但随着厚度的增加缺陷减小;2)成本高,一般用于制作低功耗器件,近年来用SOI代替,可降低成本;

需要解决的问题:提高SOS外延层的晶体完整性,降低自掺杂,使其性能接近同质硅外延层的水平并且有良好的热稳定性.

SOI技术 Silicon on Insulator Semiconductor On insulator p115~116

Def

是指在半导体的绝缘层(如二氧化硅)上, 通过特殊工艺再生长非常薄的一层硅, 在这层SOI层之上再制造电子器件.

作用

大大提高晶体管充放电速度,提高数字电路的开关速度.

特点

寄生效应小、速度快、功耗低、集成度高、抗辐射能力强等诸多优点

结构特点

在有源层和衬底层之间插入埋氧层来隔断二者的电连接

和体硅在电路结构上的主要差别

硅基器件或电路制作在外延层上,器件和衬底直接产生电连接,高低压单元之间、有源层和衬底层之间的隔离通过反偏pn结完成; 而SOI电路的有源层、衬底、高低压单元之间都通过绝缘层完全隔开,各部分的电气连接被完全消除.

挑战

材料是SOI技术发展的主要障碍之一,这个障碍目前正被逐渐清除.

常用的方法

SDB:直接键合技术

采用键合技术形成SOI结构的核心技术之一. 方法是将两个硅片通过表面的SiO2层键合在一起,再把背面用腐蚀等方法进行减薄来获得SOI结构.

键合是由吸附在两个硅片表面上的OH-在范德瓦尔斯力作用下相互吸引所引起; 在室温下实现的键合通常不牢固,所以键合后还要进行退火,键合的强度随退火温度的升高而增加; 键合后采用机械研磨或化学抛光的方法,将器件层的硅片减薄到预定厚度.

优缺点: 硅膜质量高; 埋氧厚度和硅膜厚度可以随意调整; 适合于大功率器件及MEMS技术; 硅膜减薄一直是制约该技术发展的重要障碍; 键合要用两片体硅片制成一片SOI结构,成本至少是体硅的两倍.

SIMOX (Separating by Implanting Oxide )---------注氧隔离

SIMOX是通过将氧离子注入到硅片内,再经高温退火过程消除注入缺陷而制造SOI结构的一种工艺过程.

硅膜均匀性较好,但还要经过高温退火过程,所以制备成本很高,价格非常贵. 制备的顶层硅膜通常较薄,为此,人们采用在SIMOX基片上外延的方法来获得较厚的顶层硅 SIMOX技术通常用于制备薄硅膜、薄埋氧层的SOI材料.

发展趋势和主要困难

最新趋势是采用较小的氧注入剂量 (~ 41017/cm2)获得薄埋氧层厚度:800~1000Å; 显著改善顶部硅层的质量; 降低SIMOX材料的成本; 退火温度高于1300℃,制备大面积(300mm)SIMOX材料十分困难.

Smart Cut-----智能切割

兼具有SDB和SIMOX的特点,工艺流程包括热氧化、注氢、低温键合、热处理剥离、精密抛光等.

硅片顶部硅膜的均匀性相当好,单片厚度偏差和片间偏差可控制在10nm以内,另外生产成本也可降低,因为不需要昂贵的专用大束流离子注入机和长时间的高温退火,所以这是一种极有前途的SOI制备技术,特别适用于制备薄硅膜、厚埋氧层材料.

ELTRAN (Epoxy Layer Transfer)----外延层转移

独特之处在于在多孔硅表面上生长平整的外延层,以合理的速率将多孔硅区域彻底刻蚀掉. 该技术即保留了外延层所具有的原子平整性,而且在晶体形成过程中也不产生颗粒堆积或凹坑,因此具有比其它SOI技术更为优越的性能.

SDB法通常用于制备厚埋氧层材料,其硅层的厚度取决于硅片减薄技术的发展,早期该技术只能制备厚硅层材料,后来随着BE(Back Etch)技术、CMP(Chemical Mechanical Polishing)技术以及 Bonding技术的发展,也可以用于制备极薄的顶层硅(0.1μm ). SIMOX法由于氧注入条件限制,只能用于制备薄硅层(0.1~0.4μm)和薄埋氧层(0.1~0.4μm)材料. 要获得厚硅层,必须再进行外延生长,即采用ESIMOX法; Smart Cut法由于采用了键合工艺,最适用于制备薄硅层(0.1~1μm)和厚埋氧层材料; ELTRAN法的适用范围最宽,可根据用户要求,提供从几十纳米到几十微米的硅层和埋氧层.