导图社区 vol3-28-VMX对地址翻译的支持

- 20

- 0

- 0

- 举报

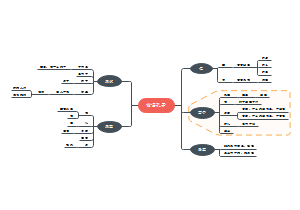

vol3-28-VMX对地址翻译的支持

VMX操作的体系结构包括两个支持地址转换的功能:虚拟处理器标识符(VPID)和扩展的页面表机制(EPT)。 VPID是一种管理线性地址转换的机制。

编辑于2022-09-16 17:08:00 上海- x86芯片

- Vol3-29-APIC虚拟化和虚拟中断

Virtualize APIC Accesses 功能可以单独开启,此时它的作用仅仅是将Guest APIC访问的VM Exit从EPT Violaton改为了APIC Access,对Guest的APIC访问仍需要以Trap-and-Emulate方式实现。

- Vol3-24-虚拟机控制结构VMCS

VMCS 的数据区包含了VMX配置信息:VMM在启动虚拟机前配置其哪些操作会触发VMExit。VMExit 产生后,处理器把执行权交给VMM 以完成控制,

- Vol3-23-VMX(Virtual Machine Extension)

系统软件可以通过CPUID指令来判断处理器是否支持VMX,如果CPUID.1.ECX.VMX[bit5] = 1,那么当前处理器支持VMX,否则,当前处理器不支持VMX功能。

vol3-28-VMX对地址翻译的支持

社区模板帮助中心,点此进入>>

- Vol3-29-APIC虚拟化和虚拟中断

Virtualize APIC Accesses 功能可以单独开启,此时它的作用仅仅是将Guest APIC访问的VM Exit从EPT Violaton改为了APIC Access,对Guest的APIC访问仍需要以Trap-and-Emulate方式实现。

- Vol3-24-虚拟机控制结构VMCS

VMCS 的数据区包含了VMX配置信息:VMM在启动虚拟机前配置其哪些操作会触发VMExit。VMExit 产生后,处理器把执行权交给VMM 以完成控制,

- Vol3-23-VMX(Virtual Machine Extension)

系统软件可以通过CPUID指令来判断处理器是否支持VMX,如果CPUID.1.ECX.VMX[bit5] = 1,那么当前处理器支持VMX,否则,当前处理器不支持VMX功能。

- 相似推荐

- 大纲

VMX对地址翻译的支持

概述

VMX包含2种支持地址翻译的特性.

virtual-processir identifiers(VPID), 负责管理线性地址的翻译

extended page-table mechanism(EPT),定义了一个地址转换层,可增强线性地址的转换

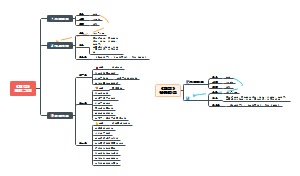

28.1 Virtual Processor Identifiers(VPID)

本节主要讲VPID的架构

原始VMX架构需要VMX transitions来清除TLBs和paging-structure的缓存. 这确保在transition之后为旧的线性地址缓存的transition不会再使用.

VPID给逻辑处理器为多个线性地址空间缓存信息提供了便利.

使用VPID时,VMX transitions会保存缓存的信息,逻辑处理器会切换到另一个线性地址空间.

逻辑处理器会将一些cached的信息用一个16bit的VPID打上标签

任何时候确定current VPID的方法

部分情况下为0000H

在特定control为1的情况下,VPID为VMCS中的另一control bit的值

VPID和PCID(processor context identifier)可以同时使用. 如果同时使用的话,处理器会将cached的信息与VPID和PCID同时联系起来,而此类信息只有在VPID和PCID同时匹配cached的信息时才被使用.

28.2 The Extended Page Table Mechanism (EPT)

EPT概述

EPT可以用来做物理memory的虚拟化.

当使用EPT时,本来要被视为物理地址的特定地址会被视为guest-physical address.

通过遍历一系列的EPT paging structures将Guest-physical address转化为可以用来访问内存的物理地址.

当“enable EPT” VM-execution control is 1时使用EPT. EPT将非根模式和在VM entry中用于事件注入的guest-physical address翻译为物理地址.

EPT paging structure与IA-32e模式下用于翻译线性地址的structure类似.

如果CR0.PG=1, 线性地址由CR3确定的paging structure翻译.当“enable EPT” VM-execution control is 1时,这些structure称为guest paging structures,如果CR0.PG为0,则不存在guest paging structures

当“enable EPT” VM-execution control is 1时,guest-physical address的Identity取决于CR0.PG

CR0.PG为0时,每个线性地址都当作guest-physical address

CR0.PG为1时,guest-physical address是那些从CR3(PDPTE)和guest-paging structures(PS bit为1)中继承下来的地址.

如果CR0.PG=1,从线性地址转化为物理地址需要使用EPT对guest-physical address进行多次翻译.线性地址的不同位段代表guest-PDE、guest-PTE、page-frame.

EPT指定访问地址时允许软件的特权,对不允许访问的地址访问会导致EPT violations,进而导致VM exits

只有当guest-physical address被用来访问memory时,处理器才会使用EPT翻译该地址.

Mov to CR3指令会使用一个guest-physical地址,该地址 是否被翻译取决于PAE paging是否在使用.

将存储在CR3中的guest-physical address 使用Mov to CR3/CR4指令载入PDPTE时,使用EPT翻译地址.

PDPTE包含guest-physical address,那些不使用这些地址访问memory和不导致EPT翻译这些地址的载入PDPTE的指令,这些地址将会在下一次访问memory时通过EPT翻译.

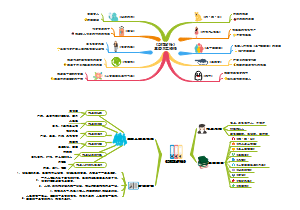

EPT翻译机制

EPT翻译时只使用每个guest-physical address的bits 47:0.最多使用4个EPT paging-structure来翻译guest-physical address.

逻辑处理器对这48位进行分区,以遍历EPT paging structure

一个4KB对齐的EPT PML4 table位于由EPTP(extended-page-table pointer)的bit 51:12指定的物理地址上.该物理地址其实是一个VM-execution control field中的值.一个EPT PML4包含512个 64bit entries,这些entry称为EPT PML4Es,使用特定规则选择一个EPT PML4E.最大能访问512GB空间的guest-physical address. Table 28-1是PML4E的format.

PML4E的作用是寻找PDPT.

一个4KB对齐的EPT PDPT位于EPT PML4E的bit 51:12指定的物理地址上.一个EPT PDPT包含512个64bit entries,这些entry称为EPT PDPTEs.用特定规则选择一个EPT PDPTE.一个PDPTE能访问guest-physical address空间1GB. EPT PDPTE的使用取决于该PDPTE的bit7. EPT PDPTE的格式在Table 28-3.

PDPTE可能映射到一个1GB的页,也有可能映射到PD.

一个EPT page-directory包含512个64bit entries. 这些entries称为PDE.使用特定规则选择一个PDE. 一个PDE访问2MB guest-physical address 空间. EPT PDE的使用取决于该PDE的bit 7.

PDE可能映射到一个2MB的页,也有可能映射到PT.

一个EPT PT包含512个64bit的PTE. 使用特定规则选择一个PTE. 每个PTE映射一个4KB的页.可以通过特定规则计算最终物理地址.

Figure 28-1

如果EPT paging structure entry的bit 2:0任意一个bit为1,则该EPT paging structure为present. 否则为not present. 翻译过程中遇到使用"not present"的EPT paging structure的guest-physical address,就会导致EPT violation(可转化为虚拟异常).

如果 “mode-based execute control for EPT” VM-execution control is 1,EPT paging structure的bit2:0或bit10任意bit为1,则为"present".

EPT引起的VM Exits

使用guest-physical address访问可能会引起EPT误配置、EPT违规、page-modification log-full event.

在翻译guest-physical address的过程中,逻辑处理器遇到一个包含不支持值的EPT paging-structure entry,就会发生EPT误配置.

当没有发生EPT误配置,但EPT paging-structure entry不允许访问guest-physical address,就会发生EPT违规.

当处理器提出一个创建page-modification log entry的需求,但是current log满了,就会导致page-modification log-full event.

这些事件都是在使用guest-physical address 访问memory的时候才会发生.(Mov to CR3?)

EPT误配置

在翻译guest-physical address的过程中,其中一个EPT paging structure有以下问题,就会导致误配置事件触发.

entry的bit0为0,bit1为1

如果处理器不支持execute-only translation, 则以下情况会导致误配置事件触发

特定control为1,bit0为0,bit10为1

entry的bit0为0,bit2为1

entry为"present",以下情况成立

A reserved bit is set

该entry为最后一层用于翻译guest-physical address的entry,且bit5:3的值为2/3/7

EPT违规

以下情况发生EPT违规

翻译guest-physical address时其中一个EPT paging-structure entry为"not present"

访问用于读数据,但是至少其中一个EPT paging structure entry的bit0为0.

访问用于写数据,但是至少其中一个EPT paging structure entry的bit1为0.

访问用于取指令,但是EPT paging structures不允许访问目的地址.

EPT 误配置和EPT违规的优先级

由EPT引起的VM exits之间的优先级、EPT引起的VM exits与其他通过线性地址访问memory导致的事件之间的优先级.

访问guest-physical address时, 是否发生EPT违规或EPT误配置取决于一个交互过程.

step1. 读EPT paging structure entry时

如果该entry为"not present", 发生EPT违规

如果该entry为"present",但是其内容没有配置正确,发生EPT误配置.

如果既是"present",又配置正确,那就取决 于该entry是否reference另一个EPT paging structure.

如果reference,那就将step1. 再执行到那个被reference的entry上

如果不reference,则该entry用于产生 最终的物理地址,那就执行step 2.

step 2. 一旦最终的物理地址被确定, 由entry提供的优先级的评估如下

如果没有访问guest-physical的权限,就会发生EPT违规

如果拥有访问guest-physical的权限,就可以使用最终的物理地址访问memory.

如果CR0.PG=1,那么线性地址的翻译 也是一个交互过程.

step 1. 尝试使用一个guest-physical address(起初该地 址位于CR3/PDPTE中)访问guest-paging structure entry.

如果由于EPT误配置/EPT违规导致访问失败, 会发生EPT-induced VM exit error.

如果没有导致EPT-induced VM exit,检查该entry的bit0

如果为0或者任何保留位被置位,则发生page fault.

如果为1或者没有保留位被置位,后续操作取决于该 entry是否reference其他guest paging structure.

如果reference,那就将step1再执 行到那个被reference的entry上.

如果不reference,该entry用于产生 最终的物理地址,那就执行step2.

step 2. 一旦最终的物理地址被确定, 由entry提供的优先级的评估如下

如果没有访问guest-physical的权限,就会发生page fault

如果拥有访问guest-physical的权限,就可以使用最终的物理地址访问memory.

如果由于EPT误配置/EPT违规无法访问memory,就会产生一个EPT-induced VM exit.

如果没有发生EPT-induced VM exit,则使用最终的物理地址访问memory.

如果CR0.PG=0, 线性地址被当做guest-physical address对待,通过EPT翻译. 如果翻译过程中没有发生EPT违规和EPT误配置,产生了一个物理地址并且确定了由EPT paging structure entry允许的优先级.如果这些优先级不允许物理地址的访问,会产生一个EPT违规. 如果允许,则使用该物理地址访问memory即可.

子叶写权限

EPT-paging structure entry可以确定memory的访问权限,但是是以1G、2M、4K为粒度的权限,sub-page-write-permissions可以确定更加精细粒度(128字节对齐的子叶)的权限.该特性还可以允许写入在其它情况下无法写入的4KB的页

“sub-page write permissions for EPT” VM-execution control 控制该特性使能.

符合子页面写权限的写访问

如果在EPT违规(section 28.2.3.2)中对一个guest-physical address的写操作不被允许,那么该地址就可以获得子页面写权限.由于其它情况导致的写操作不被允许的情况不能获得子页面写权限.

只有在一个guest-physical address通过4KB页映射并且用来映射该页的EPT PTE的bit 61为1时,才可以获得子页面写权限(大于4KB就无法获得该权限了).

对于部分memory访问,处理器无视用来映射4KB页的EPT PTE的bit 61,并且对该memory访问不提供子页访问权限.

子页写权限从不提供给以下memory访问.

在transactional region内执行的写访问

enclave对enclave's ELRANGE内地址的写访问

通过一个Intel SGX 指令对ENC(enclave page cache)的写访问

对guest-paging structure以更新已经访问的/dirty flag的写访问

当针对EPT的Accessd 和 dirty flags被使能时,处理器对guest-paging structure entry的访问

以下情况子页写权限可能不会提供.是model-specific的.

跨越2个4K页的写访问.子页写权限可能2个页都不给,也可能只给其中一个. 除非对两个页都赋予子页写权限,否则两个页都不会发生写操作.

同时涉及多个写访问的指令.子页访问权限是为基本指令设计的,如AND、MOV、OR等.

如果一个guest-physical address符合子页面写权限的要求,处理器以28.2.4的处理方式决定是否允许对该地址进行写入.

如果一个guest-physical address符合子页面写权限的要求,并且该地址被翻译为APIC-Access 页中的地址,处理器处理对该地址的写访问时会假设“virtualize APIC accesses” VM-execution control were 0. 因此推荐软件不要将被翻译为APIC-Access 页中的地址的guest-physical address为符合子页面写权限的.

确定访问权限的子页面写权限

子页写权限独立控制(individually)4KB页的32个128字节子页的写访问. guest-physical address的bit 11:7被用来确定子页.

对于每个符合子页面写权限要求的guest-physical address,存在一个64bit的sub-page permission vector(子页权限向量SPP vector). 所有同一个4K页面上的地址共享同一个SPP vector. 如果一个地址的子页号码(地址的bit11:7)为S,当且仅当sub-page permission的bit 2S被设置为1时,向该地址写入操作才被允许. SPP vector中的奇数bit必须置为0.

每个页的SPP vector都在memory中. 对于符合子页面写权限要求的guest-physical address的写操作,处理器使用以下方法定位该地址的SPP vector.

SPPTP (sub-page-permission-table pointer) VM-execution control field 中包含4KB根SPP table(SPPL4 table). guest-physical address的bit47:39确定该table中的64bit entry(SPPL4E).

SSPL4E中包含一个4KB SPPL3 table的物理地址,guest-physical address的bit38:30确定该table中的一个64bit entry,称为SPPL3E.

SSPL3E中包含一个4KB SPPL2 table的物理地址,guest-physical address的bit29:21确定该table中的一个64bit entry,称为SPPL2E.

SPPL2E中包含一个4KB SPP vector table(SPPL1 table),guest-physical address的bit20:12确定该table中的一个64bit SPP vector. 如果一个地址的子页号码(地址的bit11:7)为S,当且仅当该sub-page permission的bit 2S被设置为1时,向该地址写入操作才被允许. SPP vector中的奇数bit必须置为0.

访问这些table的memory type在 IA32_VMX_BASIC MSR的bits53:50.

针对多个在同一个4K页内的128字节子页的写访问,只有在该页的SPP vector的对应的每个子页的位置都为1时,才能允许访问.

以下措施在对2个4K页进行写访问时应用.

如果在28.2.3.2情况下,对任意一个页的写都不被允许,则该写访问可能不被允许(model-specific),即使该页符合子页面写权限的要求.

以下情况该写访问被允许.

要么在28.2.3.2情况下被允许

或者该guest-physical address符合子页面写权限的要求,且该页的SPP vector允许写.

SPPL4E, SPPL3E, or SPPL2E的bit0为有效bit,如果在访问这些entry的过程中发现某个有效bit为0,那么处理过程就会停止,逻辑处理器会产生一个SPP miss.

SPPL4E, SPPL3E, or SPPL2E的bit11:1和bit63:N(N为处理器宽度)为保留位,如果上面的处理过程中有效bit为1,但是某些保留位为设置为1,那么逻辑处理器会产生一个SPP misconfiguration.SPP vector中的奇数bit也是保留位,对这些保留位的设置也会导致SPP misconfiguration.

SPP miss和SPP misconfigration都为SPP-related event,会导致VM exits

针对EPT的已访问标志和脏标志

Intel 64架构支持在普通的paging structure entry中的已访问和脏标志.

部分处理器(MSR IA32_VMX_EPT_VPID_CAP)也支持EPT paging structure entry中的已访问和脏标志.

为EPT使能Accessd and Dirty FLAGS

设置extended-page-table pointer (EPTP)的bit 6

如果bit 6为1,则使能,且会使处理器访问guest-paging structure entry的行为被视为写访问.

任何一个在guest-physical-address translation期间使用的EPT paging structure entry, bit 8 都是 Accessed Flag.

映射一个页(而不是另一个EPT paging structure)的EPT paging structure entry,bit 9 为 dirty Flag.

当处理器使用一个EPT paging structure entry作为guest-physical-address translation的一部分时,处理器就会置该entry中的Accessed flag.

当对guest-physical address进行写操作时,处理器就会置产生最终物理地址的paging-structure entry(不是EPT PTE就是bit 7 为1 的EPT paging structure entry)的dirty flag.

PAE paging情况下,使用MOV to CR指令载入PDPTE就寄存器被视为read操作.

Accessed个dirty flag都是"sticky"的,即一旦设置为1,处理器不会自动clear,只有软件可以clear.

处理器可能会将EPT paging structure entry cache到TLBs和 paging structure caches. 这意味着如果软件将dirty/accessed flag修改为1,处理器可能不会在后续访问相关guest-physical address时修改对应的缓存中的entry的dirty/accessed flag.

页编辑日志

如果EPT的accessed/dirty flag功能被使能,那么软件可以通过page-modification logging 追踪对guest-physical address的写访问历史.

page-modification logging使能

将“enable PML” VM-execution control设置为1

当该control为1时,处理器会将entries加入到page-modification log.

page-modification log在PML address VM-execution control field中的物理地址中,是一个4K区域.

page-modification log包含512个64-bit entries,PML index VM-execution control field指明了下一个使用的entry.

在允许一次guest-physical 访问之前,处理器可能会确定首先需要给EPT设置一个accessed/dirty flag. 在该确定发生时,处理器查看PML index,如果PML index不在0-511的范围内,就会发生page-modification log-full event和VM exit,如果发生这样的情况(不在范围内),accessed/dirty flag不会被置位,同时导致该event发生的guest-physical 访问也不会发生.

如果PML index在0-511的范围内,处理器会继续以正常方式更新dirty/accessed flags

如果处理器更新了EPT的dirty/accessed flags,处理器后续会按以下步骤操作.

1. 本次访问的guest-physical address会被写入page-modification log.即,guest-physical address会被写入到8 ×PML index + PML address的物理地址中去.guest-physical address的bits 11:0 恒为0.

2. PML index -= 1

(注意:0-1=FFFFH),此时由于index为FFFFH,不在0-511范围内,则发生log-full event和VM exit.

EPT and Memory Typing

访问EPT paging-structures时确定memory type

CR0.CD(bit 30) = 0时,EPTP(VM-execution control field)的bits 2:0为memory type,0为UC(uncacheable),6为WB(write back).其它值为reserved.

CR0.CD=1时,memory type为UC.

访问经EPT paging-structure翻译得到的物理地址 时确定memory type

通过guest-physical address(经过EPT翻译的访问)的有效memory type是用于访问memory的memory type.

取决于3个因素

CR0.CD

CR0.CD=0时,有效memory type取决于最后一个用于确定最终物理地址的EPT-paging structure entry的bit 6

如果该值为0,有效memory type为EPT memory type和PAT memory type的结合.见Table 11-7,用EPT memory type代替 MTRR memory type.

如果该值为1,有效memory type为EPT memory type. PAT memory type被丢弃.

CR0.CD=1时,有效memory type为UC

最后一个用于确定最终物理地址的paging structure entry

该entry中的bits 5:3指明了EPT memory type

0=UC

1=WC

4=WT

5=WP

6=WB

其它值为保留位,导致EPT误配置.

PAT(PAGE ATTRIBUTE TABLE) memory type(取决于CR0.PG)

如果CR0.PG=0,则PAT memory type为WB

如果CR0.PG=1,则PAT memory type为IA32_PAT MSR中选择的memory type.

访问guest-physical address时,MTRR在确定memory type时没有作用.

28.3 Caching Transition Information

支持Intel® 64 and IA-32 architectures的处理器会将address-translation过程中的数据缓存到内存中以加速翻译过程.VPID和EPT特性增强了该caching 架构.

EPT定义了guest-physical address space并且定义了对该地址空间(from/to)的翻译.

会被cached的信息

translations

从linear page numbers到physical page frames的映射.

paging structure caches

将linear page number的upper bits映射到paging structure entry(用于翻译匹配这些upper bits的线性地址)的信息

当VPID和EPT被使用时,同样类似上面两类的信息 也会被cache并且依据各自的作用进行应用.

具有不同作用的信息(cached)区别如下

linear mappings

linear translations

每个线性翻译都是一个从linear page number到physical page frame 的映射,还有一些access privilege和memory type信息.

linear paging-structure-cache entries

每个线性页结构缓存条目都是一个从linear address的upper 部分到paging structure的物理地址的映射,还包含access privilege相关信息.例如,一个线性地址的bits 47:39将会映射到相应的PDPT的地址.

linear mappings不包含任何来自EPT paging structure的信息.

Guest-physical mappings

Guest-physical translations

每个guest物理翻译都是一个从guest-physical address page number到physical page frame的映射,还包含一些access privilege和memory type相关信息.

Guest-physical paging-structure-cache entries.

每个guest物理页结构缓存条目都是一个从guest-physical address到EPT paging structure 的物理地址的映射,还有access privilege相关信息.

guest-physical mappings中与access privilege和memory type相关的信息继承自EPT paging structure

combined mappings

combined translations

每个结合翻译都是一个从linear page number 到 physical page frame的映射,还包括一些access privilege和memory type相关信息.

Combined paging-structure-cache entries

每个结合页结构缓存条目都是一个从linear address的upper portion到页结构的物理地址的映射,还包括一些access privilege相关信息.

combined mappings中与access privileges and memory typing相关的信息继承自guest-paging structure和EPT paging structure.

Guest-physical mappings和combined mappings可能也包含SPP vectors和用于定位SPP vectors的数据结构

创建并使用cached translation information

当不使用EPT(包括在VMX non-root模式外)时mappings的创建

linear mappings可能会被创建

从CR3 reference的paging structures中继承,并且与current VPID和current PCID有关.

不会用从"not present"或设置了reserved bit的paging structure entries继承的信息创建linear mappings.例如,如果一个PTE为"not present",那么就不会为任何translation将会使用该PTE的linear page number创建linear mapping.

当不使用EPT时,不会创建任何guest-physical/combined mappings

当使用EPT时,mappings的创建

可能会创建guest-physical mappings

从current EPTP的bits 51:12 reference的EPT paging structures中继承,这40bits包含EPT-PML4-table的地址(EP4TA refer to的就是这40bits).新创建的guest-physical mappings与current EP4TA相关联.

可能会创建combined mappings

从current EPT4TA reference的EPT paging structures中继承. 如果CR0.PG=1,则也从CR3的当前值reference的paging structures中继承.这些combined mappings与current VPID、current PCID、current EP4TA相关联. 如果CR0.PG=0,则不会创建combined paging-structure-cache entries.

不会利用从"not present"或设置了reserved bits的guest paging-structure entries继承的信息创建combined mappings.

当使用EPT时,不会创建linear mappings

mappings的使用

如果不使用EPT(如在VMX non-root模式的外部),逻辑处理器以 以下方式使用cached mappings

对于使用linear address的access,会使用与current VPID和current PCID关联的linear mappings.可能也会使用与current VPID和current PCID关联的global TLB entries(linear mappings).

当不使用EPT时,不会使用guest-physical 或者 combined mappings.

如果使用EPT,逻辑处理器以以下方式使用cached mappings

对于使用linear address的access,可能会使用与current VPID、current PCID、current EP4TA关联的combined mappings. 也可能会使用与current VPID、current PCID、current EP4TA关联的global TLB entries(combined mappings).

Invalidating Cached Translation Information

软件对paging structures的编辑可能会导致这些structures与被处理cached的mappings之间出现内容不一致的情况. 部分操作能够invalidate处理器cached的数据,可以利用这些操作处理这种内容不一致的情况.

Operations that Invalidate Cached Mappings

架构性invalidate TLB中的entries或者与VMX operation独立的paging structure caches的Operation可以invalidate linear mappings和combined mappings.

这些操作只针对current VPID(对于combined mappings,则是对所有EP4TAs).

即使EPT在使用,针对current VPID的linear mappings也会被invalidate.

即使EPT没有在使用,针current VPID的combined mappings也会被invalidate.

EPT违规会invalidate任何被用于翻译guest-physical address并导致EPT违规的guest-physical mappings(与current EP4TA相关联)

如果上面的guest-physical address是linear address的翻译,EPT违规也会invalidate任何与current VPID、current PCID、current EP4TA相关联的linear address的combined mappings.

如果“enable VPID” VM-execution control is 0, VM entries和VM exits会invalidate与VPID 0000H的相关联的linear mappings和combined mappings. 与VPID 0000H相关联的的combined mappings会针对所有EP4TAs被invalidate.

INVVPID指令的执行会invalidate linear mappings和combined mappings.Invalidation基于指令的operands,有2种.

INVVPID type

individual-address

如果INVVPID type为0,逻辑处理器会invalidate与VPID(在INVVPID descriptor中指定的)相关联的linear mappings和combined mappings, 也会invalidate用于后续翻译线性地址的linear mappings和combined mappings(在INVVPID descriptor中指定的 ). 该VPID和线性地址的linear mappings和combined mappings对于所有PCIDs,combined mappings,所有EP4TAs,被invalidate. (该指令也有可能invalidate与其它VPID和其它linear address相关联的mappings)

single-context

如果INVVPID type为1, 逻辑处理器会invalidate所有与VPID(在INVVPID descriptor中指定的)相关联的linear mappings和combined mappings. 对于所有PCIDs,combined mappings,所有EP4TAs,与该VPID相关联的linear mappings和combined mappings被invalidate. (该指令有可能invalidate与其他VPID相关联的mappings.)

all-context

如果INVVPID type为2, 逻辑处理器invalidate除了VPID 0000H之外的所有VPID和PCID相关联的linear mappings和combined mappings.(该指令也可能invalidate 与VPID 0000H相关的linear mappings). 与所有EP4TA相关联的combined mappings也会被invalidate.

single-context-retaining globals

如果INVVPID type为3,逻辑处理器会invalidate与VPID(在INVVPID descriptor中指定的)相关联的linear mappings和combined mappings. 对于所有PCIDs,combined mappings,所有EP4TAs,与该VPID相关联的linear mappings和combined mappings被invalidate. 逻辑处理器不需要invalidate用于global translation(允许软件指定的translation在cache到TLB时得到特殊对待)的信息.(该指令有可能invalidate与其他VPID相关联的mappings.)

INVVPID descriptor

INVEPT指令的执行会invalidate guest-physical mappings和combined mappings.该Invalidation基于指令的Operands,有2种

INVEPT type

single-context

如果INVEPT type为1, 逻辑处理器invalidate所有与EP4TA(INVEPT descriptor中指定的)相关联的guest-physical mappings和combined mappings. 针对所有VPID和所有PCID,该EP4TA关联的combined mappings都会被invalidate.(该指令也可能invalidate与其他EP4TA相关联的mappings)

all-context

如果INVEPT type为2,逻辑处理器会invalidate与所有EP4TA相关联的guest-physical mappings和combined mappings. 针对所有的combined mappings,所有VPID和所有PCID,与该EP4TA相关联的guest-physical mappings和combined mappings都会被invalidate.

INVEPT descriptor

power-up或reset会invalidate所有linear mappings、guest-physical mappings、combined mappings.

不需要invalidate cached mappings的Operation

那些架构性invalidate TLB中的entries或者独立于VMX操作的paging structure caches的Operation不需要invalidate任何guest-physical mappings.

INVVPID指令不需要invalidate任何guest-physical mappings.

INVEPT指令不需要invalidate任何linear mappings.

VMX transitions不需要invalidate 任何guest-physical mappings.

如果“enable VPID” VM-execution control is 1,VMX transitions不需要invalidate任何linear mappings或者combined mappings.

VMXOFF和VMXON指令不需要invalidate任何linear、guest-physical、combined mappings.

尽管以上说不需要,但是处理器还是可能在执行上述指令时invalidate任何mappings. 即不需要,但有可能发生.

INVVPID指令的使用指南

VMM软件使用INVVPID指令的需求取决于该软件如何虚拟化memory

如果EPT没被使用,则VMM虚拟化guest-paging structure. 这样一个VMM可能会配置VMCS以达到所有或部分invalidate TLB中的entry或paging-structure的caches的Operation能够导致 VM exit.如果VMM 软件在仿真这些Operations,则不需要使用INVVPID来确保逻辑处理器的TLB和paging structure cache中的数据被正确invalidate.

软件何时使用INVVPID指令取决于页表的特定虚拟化算法.以下是一些指南

INVLPG的仿真需要INVVPID的执行,还有一些细节见SDM文档

部分invalidate所有TLB中的entry和paging-structure caches的指令(除了global transitions),需要INVVPID的执行.还有一些细节见SDM文档

部分invalidate所有TLB中的entry和paging-structure caches的指令(包括global transitions),需要INVVPID的执行.还有一些细节见SDM文档

如果EPT没被使用,逻辑处理器将所有自己创造的mappings与current VPID联系起来,并使用这些mappings翻译线性地址. 因此,VMM 不应该将该VPID使用在不同的使用不同页表的non-EPT guest上.如果这么做会导致一个guest使用属于另一个guest的translation.

如果EPT被使用,上面提到的指令将不会被配置引发VM exit,VMM 将不会对这些指令进行仿真.在这种情况下,guest软件对指令的执行会正确invalidate TLB中的相关entry和paging structures caches. 不需要INVVPID指令的执行

如果EPT被使用,逻辑处理器将所有自己创造的mappings与current EPTP的bits51:12关联起来.如果VMM在不同的guest上使用不同的EPTP,则VMM可能会对这些guest使用相同的VPID.这样做不会导致一个guest使用属于另一个guest的translation.

如果EPT在使用,以下两条指南使用更加generally

APIC-Access page相关

VMXON/VMXOFF前后INVVPID的使用

INVEPT指令使用指南

软件在对EPT paging-structure entry做了任何修改之后应该使用INVEPT type为"single-context"的INVEPT指令(同时INVEPT descriptor应该包含一个EPTP,EPTP中的值直接或间接指向被修改的EPT paging-structure entry). 还有一些细节见SDM文档

如果要实施VM entry,在VM entry之前处理器处于VMX non-root模式,并带有一个EPTP值Y,Y[6] = 0, 且Y[51:12] = X[51:12]. 那么软件在带有一个EPTP值X,且X[6]=1的VM entry之前应该使用INVEPT type为"single-context"的INVEPT指令.

软件应该在编辑了一个"present" EPT paging-structure entry以改变privilege bits0:2中的任何一位从0到1后,应该执行INVEPT指令.如果不执行该指令则会导致EPT违规.因为EPT违规会invalidate所有被导致EPT违规的访问使用的mappings,EPT违规不会在之前导致EPT违规的access再次发生后第二次被触发,即使不知执行INVEPT,也不会第二次被触发.

因为逻辑处理器不会cache任何从"not present"或误配置的EPT paging structure entries中继承的信息,因此不需要在修改了一个"not present"或误配置的EPTpaging structure entry之后执行INVEPT

如29.4.5中所说,如果软件没有正确invalidate可能从EPT paging structure中cache的信息,对APIC-access page的访问就不会导致APIC-access VM exit.如果在一个逻辑处理器上值为X的EPTP曾用过一次,那么在同一个使能EPT且EPTP值为X,且满足(a)“virtualize APIC accesses” VMexecution control值从0变为1,(b)APIC-access address被修改其中一个条件的逻辑处理器上,推荐软件使用INVEPT type为"single-context"并且INVEPT descriptor中的EPTP值为X.

在VMXON之后或VMXOFF之前的一瞬间可以使用INVEPT type为"all-context"的INVEPT指令,两种方法都可以防止在VMX操作的单独使用期间从EPT paging structure缓存的信息的潜在不良保留

在多逻辑处理器系统上,软件必须明白来自EPT paging structures entries中的信息可能会缓存在修改该entry的逻辑处理器之外的其他逻辑处理器上。将更改传播到分页结构条目的过程通常称为“ TLB击落“,关于”TLB击落“的信息在4.10.5.