导图社区 语文一年级下册第四单元

- 763

- 6

- 0

- 举报

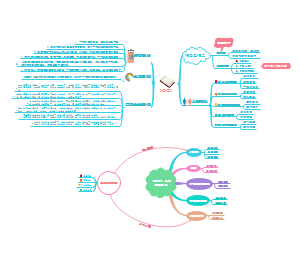

语文一年级下册第四单元

语文一年级下册第四单元,具体内容有静夜思、夜色、端午粽、彩虹、语文园地四,可以思维导图的方式给孩子们预习复习哦。

编辑于2023-03-17 18:27:43- 语文一年…

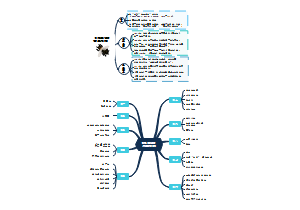

- 语文一年级下册《第三单元》

在小学语文的学习旅程中,一年级下册是一个关键的启蒙阶段。《语文一年级下册〈第三单元〉思维导图模板》宛如一位贴心的学习伙伴,为一年级学生梳理了本单元的知识脉络,助力他们轻松掌握学习重点。“小公鸡和小鸭子”通过讲述小公鸡和小鸭子互相帮助的故事,让学生明白友谊与互助的重要性,同时学习课文中的生字词和精彩对话。“树和喜鹊”则以简洁而温暖的语言,展现了从孤单到快乐的情感变化,引导学生感受友情和邻里相伴的美好。“怎么都快乐”用活泼的笔触,列举了不同人数时的快乐玩法,让学生在阅读中体会快乐的多样,并积累丰富的动词和短语。在“口语交际:请你帮个忙”板块,模板引导学生学会礼貌地寻求他人帮助,掌握“请、请问、您、您好、谢谢”等礼貌用语,提升日常交际能力。“语文园地三”更是知识的宝库,从查字典的方法教学,如音序查字法的步骤口诀,到日积月累中经典古诗《赠汪伦》的学习,再到和大人一起读“胖乎乎的小手”的温馨故事,全方位丰富了学生的知识储备。这份思维导图模板以清晰的层次和丰富的内容,将课文重点、知识点以及学习方法一一呈现。对于一年级学生来说,它是预习时的指引,能帮助他们提前了解学习内容;是复习时的帮手。

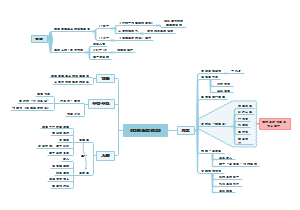

- 语文一年级下册《第一单元》主要内容

对于刚刚踏入小学学习阶段的语文一年级下册学生而言,一份清晰明了的学习思维导图就如同开启知识大门的钥匙。《语文一年级下册〈第一单元〉思维导图模板》将第一单元的丰富内容进行了全面梳理,是学生预习、复习以及巩固知识的得力助手。此模板围绕春夏秋冬展开,从字词句运用,如读记汉语拼音字母表、读写相关字词,到对四季景色描写的细致呈现,让学生感受大自然的美丽与变化。在姓氏歌部分,通过有趣的问答形式,不仅帮助学生认识常见姓氏,还激发了他们对传统文化的学习兴趣。小青蛙一课则以可爱的形象引导学生学习形声字,了解汉字的构字规律。口语交际:听故事,讲故事板块,借助经典的《老鼠嫁女》故事,培养学生的倾听与表达能力,教会他们如何记住故事内容并清晰讲述。而猜字谜环节更是增添了学习的趣味性,让学生在猜谜中感受汉字的独特魅力。模板中还贴心地给出了书写提示,帮助学生掌握正确的笔顺规则,养成良好的书写习惯。快乐读书吧推荐阅读《摇摇船》《小刺猬理发》等童谣和儿歌,鼓励学生多读书、读好书,拓宽阅读视野。这份思维导图模板适用于一年级学生,无论是课堂学习后的知识回顾,还是假期中的自主学习,都能让学生更加高效地掌握第一单元的重点内容。

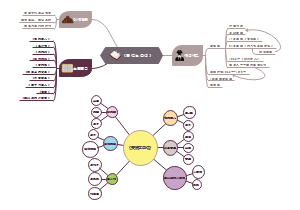

- 《论语》学而篇原文及白话文翻译

这张以《论语》学而篇原文及白话文翻译为主题的思维导图,是国学爱好者、学生群体以及教育工作者深入理解经典文化的宝藏图。在弘扬传统文化、追求知识内涵的当下,它为人们打开了通往《论语》智慧殿堂的一扇便捷之门。思维导图以《论语》学而篇的经典语句为脉络,每一条分支都对应着一句原文及其详细的白话文翻译。从“学而时习之,不亦说乎?有朋自远方来,不亦乐乎?人不知而不愠,不亦君子乎?”这一开篇之语,便引领我们走进孔子及其弟子们倡导的学习、交友与修身的境界。它不仅呈现了原文的古朴典雅,更通过通俗易懂的翻译,让读者轻松领会其中的深意。像“其为人也孝弟而好犯上者,鲜矣;不好犯上而好作乱者,未之有也。君子务本,本立而道生。孝弟也者,其为仁之本与!”这样的语句,在思维导图中清晰展现,帮助我们理解儒家思想中孝悌与仁德的根本联系。还有“巧言令色,鲜矣仁”等名言,让我们对“仁”的内涵有了更深刻的认知。对于学生而言,这是学习古典文化、提升语文素养的优质资料,能够帮助他们更好地理解文言文,积累文学知识。国学爱好者可以通过它系统梳理学而篇的内容,深入挖掘儒家思想的精髓。

语文一年级下册第四单元

社区模板帮助中心,点此进入>>

- 语文一年级下册《第三单元》

在小学语文的学习旅程中,一年级下册是一个关键的启蒙阶段。《语文一年级下册〈第三单元〉思维导图模板》宛如一位贴心的学习伙伴,为一年级学生梳理了本单元的知识脉络,助力他们轻松掌握学习重点。“小公鸡和小鸭子”通过讲述小公鸡和小鸭子互相帮助的故事,让学生明白友谊与互助的重要性,同时学习课文中的生字词和精彩对话。“树和喜鹊”则以简洁而温暖的语言,展现了从孤单到快乐的情感变化,引导学生感受友情和邻里相伴的美好。“怎么都快乐”用活泼的笔触,列举了不同人数时的快乐玩法,让学生在阅读中体会快乐的多样,并积累丰富的动词和短语。在“口语交际:请你帮个忙”板块,模板引导学生学会礼貌地寻求他人帮助,掌握“请、请问、您、您好、谢谢”等礼貌用语,提升日常交际能力。“语文园地三”更是知识的宝库,从查字典的方法教学,如音序查字法的步骤口诀,到日积月累中经典古诗《赠汪伦》的学习,再到和大人一起读“胖乎乎的小手”的温馨故事,全方位丰富了学生的知识储备。这份思维导图模板以清晰的层次和丰富的内容,将课文重点、知识点以及学习方法一一呈现。对于一年级学生来说,它是预习时的指引,能帮助他们提前了解学习内容;是复习时的帮手。

- 语文一年级下册《第一单元》主要内容

对于刚刚踏入小学学习阶段的语文一年级下册学生而言,一份清晰明了的学习思维导图就如同开启知识大门的钥匙。《语文一年级下册〈第一单元〉思维导图模板》将第一单元的丰富内容进行了全面梳理,是学生预习、复习以及巩固知识的得力助手。此模板围绕春夏秋冬展开,从字词句运用,如读记汉语拼音字母表、读写相关字词,到对四季景色描写的细致呈现,让学生感受大自然的美丽与变化。在姓氏歌部分,通过有趣的问答形式,不仅帮助学生认识常见姓氏,还激发了他们对传统文化的学习兴趣。小青蛙一课则以可爱的形象引导学生学习形声字,了解汉字的构字规律。口语交际:听故事,讲故事板块,借助经典的《老鼠嫁女》故事,培养学生的倾听与表达能力,教会他们如何记住故事内容并清晰讲述。而猜字谜环节更是增添了学习的趣味性,让学生在猜谜中感受汉字的独特魅力。模板中还贴心地给出了书写提示,帮助学生掌握正确的笔顺规则,养成良好的书写习惯。快乐读书吧推荐阅读《摇摇船》《小刺猬理发》等童谣和儿歌,鼓励学生多读书、读好书,拓宽阅读视野。这份思维导图模板适用于一年级学生,无论是课堂学习后的知识回顾,还是假期中的自主学习,都能让学生更加高效地掌握第一单元的重点内容。

- 《论语》学而篇原文及白话文翻译

这张以《论语》学而篇原文及白话文翻译为主题的思维导图,是国学爱好者、学生群体以及教育工作者深入理解经典文化的宝藏图。在弘扬传统文化、追求知识内涵的当下,它为人们打开了通往《论语》智慧殿堂的一扇便捷之门。思维导图以《论语》学而篇的经典语句为脉络,每一条分支都对应着一句原文及其详细的白话文翻译。从“学而时习之,不亦说乎?有朋自远方来,不亦乐乎?人不知而不愠,不亦君子乎?”这一开篇之语,便引领我们走进孔子及其弟子们倡导的学习、交友与修身的境界。它不仅呈现了原文的古朴典雅,更通过通俗易懂的翻译,让读者轻松领会其中的深意。像“其为人也孝弟而好犯上者,鲜矣;不好犯上而好作乱者,未之有也。君子务本,本立而道生。孝弟也者,其为仁之本与!”这样的语句,在思维导图中清晰展现,帮助我们理解儒家思想中孝悌与仁德的根本联系。还有“巧言令色,鲜矣仁”等名言,让我们对“仁”的内涵有了更深刻的认知。对于学生而言,这是学习古典文化、提升语文素养的优质资料,能够帮助他们更好地理解文言文,积累文学知识。国学爱好者可以通过它系统梳理学而篇的内容,深入挖掘儒家思想的精髓。

- 相似推荐

- 大纲

语文一年级下册 《第四单元》

8.静夜思

朗读课文。背诵课文。

唐•李白

床前明月光,

疑是地上霜。

举头望明月,

低头思故乡。

9.夜色

朗读课文。

我从前胆子很小很小,

天一黑就不敢往外瞧。

妈妈把勇敢的故事讲了又讲,

可我一看窗外心就乱跳……

爸爸晚上偏要拉我去散步,

原来花草都像白天一样微笑。

从此再黑再黑的夜晚,

我也能看见小鸟怎样在月光下睡觉……

读一读,记一记。

胆子、胆量、大胆

勇敢、勇气、勇士

原来、草原、高原

微笑、微小、微风

10.端午粽

朗读课文,注意读好长句子。

一到端午节,外婆总会煮好一锅粽子,盼着我们回去。

粽子是用青青的箬竹叶包的,里面裹着白白的糯米,中间有一颗红红的枣。外婆一掀开锅盖,煮熟的粽子就飘出一股清香来。剥开粽叶,咬一口粽子,真是又黏又甜。

外婆包的粽子十分好吃,花样也多。除了红枣粽,还有红豆粽和鲜肉粽。我们在外婆家美滋滋地吃了之后,外婆还会装一小篮粽子要我们带回去,分给邻居吃。

长大了我才知道,人们端午节吃粽子,据说是为了纪念爱国诗人屈原。

你知道关于端午节或粽子的故事吗?和同学说一说。

端午节的起源——纪念屈原

端午节源于纪念屈原。屈原,是春秋时期楚怀王的大臣。他倡导举贤授能,富国强兵,力主联齐抗秦,遭到贵族子兰等人的强烈反对,屈原遭馋去职,被赶出都城,流放到沅、湘流域。他在流放中,写下了忧国忧民的《离骚》、《天问》、《九歌》等不朽诗篇,独具风貌,影响深远。

公元前278年,秦军攻破楚国京都。屈原眼看自己的祖国被侵略,心如刀割,但是始终不忍舍弃自己的祖国,于五月五日,在写下了绝笔作之后,抱石投汨罗江身死,以自己的生命谱写了一曲壮丽的爱国主义乐章。

传说屈原死后,楚国百姓哀痛异常,纷纷涌到汨罗江边去凭吊屈原。渔夫们划起船只,在江上来回打捞他的真身。有位渔夫拿出为屈原准备的饭团、鸡蛋等食物地丢进江里,说是让鱼龙虾蟹吃饱了,就不会去咬屈大夫的身体了。

人们见后纷纷仿效。一位老医师则拿来一坛雄黄酒倒进江里,说是要药晕蛟龙水兽,以免伤害屈大夫。后来为怕饭团为蛟龙所食,人们想出用楝树叶包饭,外缠彩丝,发展成粽子。

以后,在每年的五月初五,就有了龙舟竞渡、吃粽子、喝雄黄酒的风俗;以此来纪念爱国诗人屈原。

11.彩虹

朗读课文,注意读好长句子。

雨停了,天上有一座美丽的桥。

爸爸,你那把浇花用的水壶呢?如果我提着它,走到桥上去,把水洒下来,那不就是我在下雨了吗?你就不用挑水浇田了,你高兴吗?

妈妈,如果我拿着你梳头用的那面镜子呢?如果我拿着它,走到桥上,天上不就多了一个月亮吗?我拿着圆圆的月亮照着你梳头,你高兴吗?

哥哥,你系在门前树上的秋千呢?如果我把它挂在彩虹上,坐着秋千荡来荡去,花裙飘啊飘的,不就成了一朵彩云吗?你看见了,高兴吗?

读一读,说一说。

荡来荡去、飘来飘去、游来游去、跑来跑去

我也能说这样的词语。

走来走去,飞来飞去,跳来跳去,直来直去

语文园地四

识字加油站

我来读,你来指。

眉毛、鼻子、嘴巴、脖子、手臂、肚子、小腿、脚尖

字词句运用

读一读

胆子、粽子、镜子、爸爸、妈妈、哥哥、故事、月亮、时候

书写提示

笔顺规则:

点在正上方或左上方,先写点。

点在右上方,后写点。

日积月累

寻隐者不遇

唐 贾岛

松下问童子,

言师采药去。

只在此山中,

云深不知处。

和大人一起读

妞妞赶牛

妞妞赶牛河边走,

牛牛要吃河边柳,

妞妞护柳扭牛走,

牛牛扭头顶妞妞,

妞妞拗不过牛牛,

低头捡起小石头,

吓得牛牛扭头走。