导图社区 数字电子技术

- 916

- 61

- 14

- 举报

数字电子技术

数字电子技术知识点。教材:《数字电子技术基础》 阎石 第6版 高等教育出版社,喜欢的可以点个赞收藏一下哟~

编辑于2023-06-11 20:44:02 江苏省- 数电

- 电子

- 数字电路

- 数字系统设计

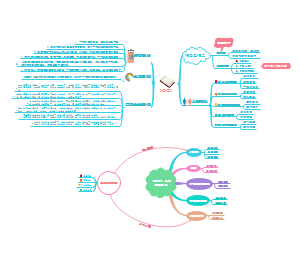

电子信息大学生竞赛知识(数学建模、电子设计) 含5个作品

电子信息大学生竞赛知识(数学建模、电子设计) 含5个作品电子信息大学生竞赛知识,包括数学建模竞赛、电子设计竞赛等

【全】电子信息专业课 211本科课堂笔记 含10个作品

【全】电子信息专业课 211本科课堂笔记 含10个作品【全】电子信息专业课,211本科课堂笔记,内容详尽,鞭辟入里,深入浅出

电子信息重点专业课 211本科课堂笔记 含6个作品

电子信息重点专业课 211本科课堂笔记 含6个作品电子信息重点专业课知识点整理,211本科课堂笔记,内容详尽,鞭辟入里,深入浅出

- 微机原理与接口技术

微机原理与接口技术知识点总结。主要内容包括:第0章 计算机基础知识,第1章 微机技术概述,第2章 8051微控制器硬件结构,第3章 8051指令系统与汇编程序设计,第4章 8051的C语言与程序设计,第5章 中断系统,第6章 定时器/计数器等。导图主要基于浙江大学王晓萍老师的课程。适用于电子、通信、自动化等专业的学生。

- 模拟电子技术基础

模拟电子技术(模拟电路)知识点总结,内容主要来源于上海交通大学郑益慧教授的课程。包括前五章的内容,涵盖常用半导体器件、常用放大电路、多级放大电路、放大电路频响等。教材:《模拟电子技术基础(第五版)》高等教育出版社,童诗白等主编。适用于电子、通信、电气等专业的学生。

- 通信原理

通信原理知识点总结,包括确知信号、随机过程、信道、模拟调制系统、数字基带传输系统、数字带通传输系统、模拟信号的数字传输(信源编码)等。适用于通信、电子信息等专业的学生。 从确知信号到随机过程,深入解析数字与模拟传输系统关键点:1调制技术对比线性调制与非线性调制的本质差异,角度调制的抗噪声优势2数字传输核心码间串扰对误码率的影响,基带与带通系统设计要点3模拟信号数字化抽样、量化、编码三步骤,重点掌握A律13折线PCM规则涵盖信道特性、功率谱分析等基础理论。

数字电子技术

社区模板帮助中心,点此进入>>

电子信息大学生竞赛知识(数学建模、电子设计) 含5个作品

电子信息大学生竞赛知识(数学建模、电子设计) 含5个作品电子信息大学生竞赛知识,包括数学建模竞赛、电子设计竞赛等

【全】电子信息专业课 211本科课堂笔记 含10个作品

【全】电子信息专业课 211本科课堂笔记 含10个作品【全】电子信息专业课,211本科课堂笔记,内容详尽,鞭辟入里,深入浅出

电子信息重点专业课 211本科课堂笔记 含6个作品

电子信息重点专业课 211本科课堂笔记 含6个作品电子信息重点专业课知识点整理,211本科课堂笔记,内容详尽,鞭辟入里,深入浅出

- 微机原理与接口技术

微机原理与接口技术知识点总结。主要内容包括:第0章 计算机基础知识,第1章 微机技术概述,第2章 8051微控制器硬件结构,第3章 8051指令系统与汇编程序设计,第4章 8051的C语言与程序设计,第5章 中断系统,第6章 定时器/计数器等。导图主要基于浙江大学王晓萍老师的课程。适用于电子、通信、自动化等专业的学生。

- 模拟电子技术基础

模拟电子技术(模拟电路)知识点总结,内容主要来源于上海交通大学郑益慧教授的课程。包括前五章的内容,涵盖常用半导体器件、常用放大电路、多级放大电路、放大电路频响等。教材:《模拟电子技术基础(第五版)》高等教育出版社,童诗白等主编。适用于电子、通信、电气等专业的学生。

- 通信原理

通信原理知识点总结,包括确知信号、随机过程、信道、模拟调制系统、数字基带传输系统、数字带通传输系统、模拟信号的数字传输(信源编码)等。适用于通信、电子信息等专业的学生。 从确知信号到随机过程,深入解析数字与模拟传输系统关键点:1调制技术对比线性调制与非线性调制的本质差异,角度调制的抗噪声优势2数字传输核心码间串扰对误码率的影响,基带与带通系统设计要点3模拟信号数字化抽样、量化、编码三步骤,重点掌握A律13折线PCM规则涵盖信道特性、功率谱分析等基础理论。

- 相似推荐

- 大纲

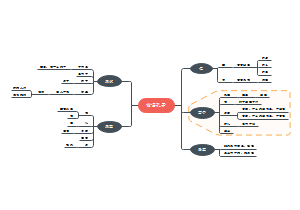

数字电子技术

第一章:数制和码制

一、 概述

信号

模拟信号

数字信号

数字信号的表示方式

0,1

H,L

数字波形

二、 几种常用的数制

名词解释

基数:该进位制中可能用到的数码个数

位权

十进制D

二进制B

八进制O

十六进制H

三、 不同数制间的转换

二转十:按权展开

十转二:

整数部分:基数连除取余

小数部分:基数连乘取整

(44.375)D=(101100.011)B

二转十六:四位并一位

十六转二:一位拆四位

八转二:一位拆三位

十六、十互转:二进制作为过渡

四、 二进制算术运算

原码反码补码

减一个数=加上其补码

补码运算:将两个加数的符号位和来自最高位数的字位的进位相加,结果就是和的符号

五、 几种常用的编码

BCD码:用四位二进制数表示十进制的0~9

常考!

常用英文

MSB:Most Significant Bit,最高加权位,二进制最左边

LSB:Least Significant Bit,最低有效位,二进制最右边

Nibble:Nibble at,四位二进制数

Parity Bit:奇偶校验位

格雷码(Gray Code)

定义:相邻两组编码仅有一位不同(又称循环码)

背景:数字系统以非常快的速度运行,并对数字输入中发生的变化作出反应。当多个输入条件同时发生变化时,情况可能会被误解并导致错误的反应

作用:减少数字电路误解不断变化的输入的可能性

G1:比较B2,B1

相同则为0

相异则为1

G0:比较B1,B0

ASCII码:7位二进制代码,共有128种状态,代表128种字符

第二章:逻辑代数基础

一、 概述

数字电路:又称逻辑电路,研究电路的输入输出之间的逻辑关系

逻辑代数:又称布尔代数/开关代数,为研究工具

逻辑变量:用字母表示,取值只有0/1,表状态而非大小

二、 三种基本运算

与逻辑(与运算)

决定事件(Y)发生的所有条件(A,B,C)均满足时,Y才发生

Y=A·B·C

(中间是点,可以省略)

与门

或

决定事件(Y)发生的条件(A,B,C)一个或多个满足时,Y就发生

Y=A+B+C

(加号读作“或”)

或门

非

A满足时,Y不发生;A不满足时,Y发生

Y=A',或

非门

常用的逻辑运算

与非

Y=(A·B)',或

或非

Y=(A+B)'

异或

相异输出1,相同输出0

同或

相异输出0,相同输出1

与或非

三、 公式

基本公式

1. 0-1律

2. 互补律

3. 重叠律

4. 还原律(双重否定律)

基本定理

1. 交换律

2. 结合律

3. 分配律

注意第二个分配律

4. 反演律(摩根定律)

活用两次取反, 可得到最简表达式

1、最简与或表达式

2、最简与非-与非表达式

两次取反

内层去非号时变成与非式

外层非号不去

3、最简或与表达式

两次取反

内层去非号时变成与非式,继续分配得与或式

(内层可以写作反函数, 如果Y非最简可以先不化简, 只化简Y'结果一样)

外层去非号得或与式

4、最简或非-或非表达式

在或与式基础上,再两次取反

内层去非号时变成或非式

外层非号不去

常用公式

1. A+AB=A

2. 吸收律

A+A'B=A+B

A(A'+B)=AB

分配律2可推导

A'+AB=A'+B

A'(A+B)=A'B

3. AB+AB'=A

(A+B)(A+B')=A

4. A(A+B)=A

5. 冗余定律/多余项定理/包含律

AB+A'C+BC=AB+A'C

AB+A'C+BCD=AB+A'C

D:“其他项”

(A+B)(A'+C)(B+C)=(A+B)(A'+C)

(A+B)(A'+C)(B+C+D)=(A+B)(A'+C)

6. A·(A·B)'=A·B'

A'·(A·B)=A'

证明:摩根律+公因子

四、 基本定理

代入定理

将一个变量用同一个逻辑代数代替,仍成立

反演定理

对Y,与或互换,01互换,变量取反, 得到反函数(补函数)Y'

“非”不变

运算优先级高的先变

先给“与”加上括号

对偶定理

对Y,与或互换,01互换,变量不变, 得到对偶式YD

若两个逻辑式相等,则对偶式也相等

五、 逻辑函数及其表示方法

逻辑函数

输出逻辑变量,输出运算结果

输出与输入之间的函数关系 Y=F(A,B,C...)

逻辑函数表示方法 (可以互相转换)

1. 逻辑真值表

快速书写:二进制依次增加1

2. 逻辑函数式(逻辑代数式)

通常采用“与或”的形式

3. 逻辑图

4. 波形图

5. 卡诺图及硬件描述语言

转换方法

真值表->逻辑函数式

看Y为1的项,若事件为0则写作“非“,写“与或式”

例:

逻辑函数式->真值表

逐一代入,列表

逻辑函数式->逻辑图

图形符号代替运算符号

事件引出两路(一路原事件一路非)

注意交点处加点

例:

逻辑图->逻辑函数式

从输入端到输出端逐级写出每个图形符号对应的逻辑式

波形图->真值表

逐个写出即可

逻辑函数的两种标准形式

最小项表达式 (标准与或表达式)

最小项 (标准积项)

定义

乘积项

变量以原变量或反变量的形式出现

变量仅出现一次

例:

编号依据:原为1,非为0,二进制转换成十进制

数目:n个变量可组成2^n个最小项

性质

任意一个最小项,只有一组变量取值使其值为1

(与,都真才真)

任意两个不同的最小项乘积必为0

(错开了)

全部最小项的和必为1

相邻性:两个最小项仅有一个因子不同,称有相邻性 (这两个相加时能合并,消去一个因子)

任何一个逻辑函数都可以表示成唯一的一组最小项之和

配项

配项公式

A+A'=1

缺少变量的用这个补

A(B+C)=AB+AC

带括号的用这个拆

例:

注意sigma写法

sigma d(10,11,...):无关项

如果列出了函数的真值表,则只要将函数值为1的那些最小项相加,即得函数的最小项表达式

最大项表达式 (标准或与表达式)

最大项 (标准和项)

定义

乘积项

变量以原变量或反变量的形式出现

仅出现一次

数目:n个变量可组成2^n个最小项

性质

任何一个逻辑函数都可以表示成唯一的一组最大项之积

配项

每个变量不全的积补上+AA'

最小项与最大项的关系

相同编号的最小项和最大项存在互补关系

一个非运算后与另一个相等

若干个最小项之和表示的表达式Y,其反函数 Y'可用等同个与这些最小项相对应的最大项之积表示

六、 逻辑函数的化简方法

公式化简法

并项法:AB+AB'=A

(把A提出来,B或上本身的非等于1)

公因式外,其余变量本身有原有非时适用

吸收法:A+AB=A

(把A提出来,或1等于1)

公因式单独成一项时适用

能提则提

消项法:AB+A'C+BC=AB+A'C

(冗余定理,BC项消掉)

3项,一变量本身有原有非

完备则消

消因子法:A+A'B=A+B

(分配律,把第一项的A代进第二项,A或上本身的非等于1)

2项,一变量本身有原有非且单独成项

考虑因子

配项法:A+A=A,A+A'=1

(或上本身等于本身,或上本身的非等于1)

多项,或上相同的一项,方便凑公因式提出来

卡诺图化简法 (Karnauph Map)

n变量最小项的卡诺图:将n变量的全部最小项各用一个小方块表示,并使具有逻辑相邻性的最小项在几何位置上相邻排列

逻辑相邻项:仅有一个变量不同,其余变量均相同的两个最小项

左右、上下

每一行首尾

每一列首尾

卡诺图的表示

一变量

二变量

推荐写法

注意第三个是11,因为相邻项要相邻排列

三变量

四变量

快速书写最小项位置:按照二进制顺序

用卡诺图表示逻辑函数

方法一

步骤

把已知逻辑函数式化为最小项之和的形式

将函数式中包含的最小项在卡诺图对应的方格中填1,其余方格中填0

例题

(繁琐)

方法二

根据函数式直接填卡诺图

例题

用卡诺图化简逻辑函数

依据:逻辑相邻性的最小项可以合并

规则:能够合并在一起的最小项是2^n个

6个最小项时,不能圈圈

2^n个最小项合并,消去n个变量

最简:圈的数目越少越简,圈内的最小项越多越简

注意:卡诺图中所有的1都必须圈到,不能合并的1必须单独画圈;每个圈中至少有1个最小项仅被圈过一次,以免出现多余项

圈0:得到原函数的反函数

利用卡诺图之间的运算化简逻辑函数

题2.22,2.23

七、 具有无关项的逻辑函数化简

无关项:φ/×,看作0/1皆可

约束项:恒等于0的项

任意项:在实际应用中是0/1对结果无影响

例

第三章:门电路

概述

正逻辑:高电平表示逻辑1、低电平表示逻辑0

负逻辑:高电平表示逻辑0、低电平表示逻辑1

集成电路

1. 小规模(SSI)

门电路<10个

2. 中规模(MSI)

10~100

3. 大规模(LSI)

100~10000

4. 超大规模(VLSI)

10 000~100 000

5. 甚大规模(ULSI)

>100 000

半导体二极管门电路

半导体二极管的开关特性

(1)二极管与门

第二行:“优先导通”

D1压差5V大,导通;D2压差2V小,不导通

Y点电压即导通电压为0.7V

(2)二极管或门

CMOS门电路

MOS管的开关特性

结构和工作原理

G:栅极

D:漏极

S:源极

基本开关电路

(化简)

TTL电路:有电流,故输入端电阻存在压降; MOS管(CMOS电路):无电流,故输入端电阻无压降

P142 题3.11

电阻分级:>2kΩ大,<200Ω小

CMOS反相器工作原理

电路结构(3)(非门)

NMOS箭头向里,PMOS箭头向外

加在左侧的(里)电压大于开启电压,NMOS导通,PMOS截止

CMOS:意为互补

vi=1时,NMOS导通,PMOS截止,故vo=0

vi=0时,NMOS截止,PMOS导通,故vo=1

典型芯片:74LS04

凹口朝左放置

最高脚(14)接VCC,一半脚(7)接GND

"74":由晶体管组成;"C":MOS管

08与门,32或门,04非门,00与非门

其他类型CMOS门电路

其他逻辑功能的CMOS门电路

与非门

74LS00:4个2输入与非门

74LS20:2个4输入与非门

或非门

74LS02

与或非门

74LS51

带缓冲级的CMOS门电路

(4)漏极开路输出门电路(OD门)

“线与”:直接将门电路连在一起,会产生瞬时大电流,烧坏电路

OD门:Open Drain,将D极开路了

例:OD输出与非门

OD门输出端可直接连接实现线与,需加一上拉电阻

接VDD,故称OD门,若接VCC则称OC门

OC门:栅极开路

(5)CMOS传输门

C=1,C'=0时导通,否则截止(呈高阻态)

(注意带圈为低电平0导通)

左输入右输出/右输入左输出 都可以(就是个门)

(6)三态门

三态:低/高/高阻态Z

高组态波形:标个Z

先看使能端EN,若使能端不导通,则输出高阻态Z

使能端置0时导通,去掉使能端就是个非门

加个倒三角就是三态门

CMOS电路的特点

TTL门电路

双极型三极管的开关特性

结构

基本开关电路

开关等效电路

动态开关特性

三极管反相器

TTL反相器

电路结构和工作原理

其他类型的TTL门电路

TTL数字集成电路的各种系列

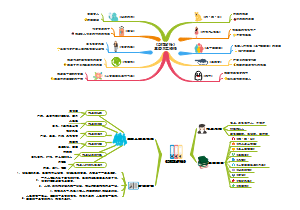

第四章:组合逻辑电路

概述

数字电路

组合逻辑电路:任一时刻的输出仅取决于该时刻的输入,与电路原来的状态无关

时序逻辑电路:任一时刻的输出不仅取决于现时的输入,而且还与电路原来状态有关

框图

不包含存储单元,仅由各种门电路组成

分析和设计方法

分析方法

步骤

1. 组合逻辑电路图

2. 写出逻辑表达式

3. 化简

化成比较清爽的,易列真值表的

4. 列真值表

观察后再写取值,不要逐项写出

5. 说明功能

例子

1.

2.

3.

4.

5. 功能:三人表决电路(只要有2票或3票同意,表决就通过)

设计方法

步骤

与分析方法相反

常要求用与非门设计,故常用卡诺图化简,得到与或表达式,再用两次取反得到与非表达式

常用组合逻辑电路

编码器 (Encoder)

编码:用二进制代码表示某一信息(文字、数字、符号)的过程

二进制编码器

输入端:2^n;输出端:n

(1)普通编码器

任何时刻只允许输入一个编码信号

3位二进制(8线-3线)编码器

高电平有效

门电路:三个或门

(2)优先编码器 (Priority Encoder)

允许同时输入两个以上编码信号,编码时只对优先权最高的进行编码

顶部加“非”,低电平有效

S'

控制键

低电平有效

I7~I0

“优先”:I7优先级最高,I0最低

I7更优先,故I7取0(有效)时其他位无关

YS',YEX'

用以区分Y2'Y1'Y0'取111的三种情况

取11:不能工作

取10:工作,有输入,编码状态

取01:工作,无输入

YS':选通输出端

取低时,表示电路工作,且无编码输入

YEX':扩展端

取低时,表示电路工作,且有编码输入

8线-3线优先编码器74LS148

中规模集成电路(几十个门)

(3)二-十进制编码器

输入端10个,输出端4个,也称10线-4线编码器

74HC147、74LS147

输入输出均低电平有效

中规模集成电路

74HC是兼容CMOS电平的,供电3~12V

74LS是兼容TTL电平的,供电4.5~5.5V

控制端扩展功能举例

用两片8线-3线,级联得到16线-4线优先编码器

第一片为高优先权

只有(1)无编码输入(YS'=0)时,(2)才允许工作

低3位输出应是两片的输出的“或”

译码器 (Decoder)

译码:将二进制代码翻译成对应的输出信号的过程,译码是编码的逆过程

二进制译码器

输入端:2^n;输出端:n

2^n个输出中只有一个为1(或为0),其余全为0(或为1)

(1)简单的3线-8线译码器

(2)带输入控制端的译码器 (最小项译码器)

S1,S2,S3

片选输入端/附加控制端

可用以多片连接扩展译码器

A2,A1,A0

地址输入端

当S2'=S3'=0时,S1的数据只能由A2A1A0所指定的线输出

GS = S1S2S3 = S1(S2'+S3')' = 1时,即S1=1,S2'+S3'=0时,电路处于工作状态,否则输出封锁在高电平

3线-8线译码器74HC138

(3)二-十进制译码器

输入端4,输出端10

将输入BCD码的10个代码译成10个高、低电平的输出信号

BCD码以外的伪码,输出均无低电平信号产生

取1010~1111这6个码时,输出均为1(拒绝伪码功能)

10线-4线译码器74HC42

(4)显示译码器

数字、文字、符号代码->译码器->显示器

例:半导体数码管

共阴/共阳

例:七段显示译码器74LS48

LT':灯测试输入,全亮

置0时输出全为1

RBI':灭零输入

BI'/RBO':灭灯输入/灭零输出

RBI和RBO配合使用,可以实现前后多余的0不显示

译码器的应用

1.

2.

3->8

3.

译码器设置全减器

题4.14

数据选择器 (Multiplexers)

定义:根据需要将多路信号中选择一路送到公共数据线上的逻辑电路(又称多路开关)

输入端:2^n个,输出端:1个

2选1数据选择器

1. 真值表

A:地址变量,Address

“控制端”

D:数据变量,Data

2. 逻辑式

3. 电路图

4. 集成化

SEL控制端

4选1数据选择器

真值表->逻辑式->电路图->集成化

1.

2.

3. 电路图略

4.

常用74HC153,双4选1数据选择器

S'使能控制端

8选1数据选择器

74HC151

“74”打头:表示内部由TTL(晶体管)组成

“CC”打头:表示内部由MOS管组成

用数据选择器设计组合逻辑电路

1. 逻辑函数(题干要求)

2. 确定数据选择器:3个变量,故选用4选1,74HC153

3. 确定地址变量:A1=A,A0=B

“高对高”

4. 求Di

1. 公式法

易理解但做起题来费眼

2. 图形法

好用!

5. 画连线图

例4.3.6

74HC151

Di都为1/0

74HC153

Di中含C(第三个变量)

题4.22(答案P219)

加法器 (Adder)

1位加法器

半加器 (Half Adder, HA)

半加运算不考虑从低位来的进位

2输入,2输出

全加器 (Full Adder)

相加过程中,既考虑加数、被加数又考虑低位的进位

双全加器74LS283

3输入,2输出

多位加法器

串行进位加法器

低位全加器进位输出->高位全加器进位输入

用全加器实现4位二进制数相加

注意:CI=0,即没有进位

优缺点

优点:电路结构简单

缺点:运行速度慢(每一位结果需等待前一位的进位产生)

超前进位加法器

优缺点

优点:运算时间缩短

缺点:电路复杂程度增加

74HC283

例

减去一个数,等于加上它的补码

数值比较器 (Magnitude Comparator)

比较两数,输出大于/小于/等于

1位数值比较器

A>B时Y1=1;A<B时Y2=1;A=B时Y3=1

4位数值比较器

74HC85

级联输入:指前四位相等后,比较后四位,得到结果

若只有4位,I(A>B)=I(A<B)=0,I(A=B)=1

若多于4位,向第二片输出低位的进位结果

例:用两片74LS85组成一个8位数值比较器

(1)输出低位进位的结果给(2)

竞争-冒险现象

概念

在组合电路中,当输入信号的状态改变时,输出端可能会出现不正常的干扰信号,使电路产生错误的输出

原因

门电路的延迟时间

检查方法

消除方法

第五章:触发器

概述

触发器 (Flip-Flops, FF)

概念:能够存储1位二值信号的基本单元电路

特点

有两个稳定的状态,0和1

适当输入信号作用下,可从一种状态翻转到另一种;输入信号取消后,能将获得的新状态保存下来

现态与次态

现态(原态):Q(Q^n-1)

次态:Q*(Q^n)

逻辑功能描述方法

功能表(特性表)

特性方程

状态图

波形图

触发器分类

按结构

SR锁存器

电平触发的触发器

脉冲触发的触发器

边沿触发的触发器

按逻辑功能(更常见)

SR触发器

JK触发器

D触发器

T和T'触发器

电路结构、动作特点

1. SR锁存器 (基本RS触发器,RS Latch)

或非门

分析:或非门看1,只要输入有1,输出即为0

如下表第二行,SD置1,则Q'输出0;RD为0,Q'再反馈输入0,则Q输出1

功能表

RD:Reset,直接复位端(置0端)

R、S都为1时,Q、Q'都为0,不合相反的逻辑

特性方程

所有SR触发器都是这个

波形图

注意:RS同时由1变为0时,Q为不定态,画×

画波形时应注意最下面是Q',不是Q*(Q的次态)

画Q'时注意不定态,其余将Q取反即可

与非门

功能表

波形图

2. 电平触发的触发器 (同步触发器) (Level-Sensitive)

电平触发SR触发器

CLK:“电平触发”

作图注意:若开始CLK=0,则Q默认为0;不定态先保持,同时变1再不定

仅在CLK为1时输出会发生改变

上升沿也称正边沿,下降沿也称负边沿

题5.4

CLK上升沿来临,RS同为1,Q和Q'为1,不合相反的逻辑

带异步(低电平触发)置位、复位端的电平触发SR触发器

D锁存器

不存在不定态

特征方程:Q*=D

3. 脉冲触发的触发器 (主从触发器) (Master-Slave)

主从SR触发器

有时要求画Qm的波形,参考同步触发器即可

题5.10

注意CLK下降沿来临时输出才发生改变,否则保持

“延迟触发”

考察CLK=1时的状态,然后在下降沿到来时就此状态而改变(与电平触发的触发器的区别)

“正脉冲触发”

下降沿来临,RS同为1时,Q为不定态,画×

这里不需要RS同时从0回到1,仍然为不定态。可以理解为CLK的优先级更高。(课本原话:当CLK的有效电平消失后,或者SR端的高电平同时回到低电平时,不能确定触发器的次态)

每个CLK周期,输出状态只能改变一次

CLK=1时,主按SR反转,从保持

CLK下降沿到达时,主保持,从根据主的状态反转

主从JK触发器

把上次的输出加入反馈,决定输入

CLK=0时,Qm不变,从触发器工作

CLK=1时,主触发器工作,从触发器保持

没有不定态

特性方程

推导

S=JQ',R=KQ

代入SR触发器特性方程:Q*=S+R'Q

列真值表,卡诺图化简

主从SR,主为同步SR,clk=1的全部时间里输入信号对主都起控制作用;但主从JK在clk高电平期间,主只可能翻转一次(“一次翻转”)

原因:输出的反馈把输入锁住了

逻辑符号

只要看到右边有这个“小直角”,就是主从触发器

因为需要等到CLK的有效电平消失后(即回到低电平),输出状态才改变,所以也把这种触发方式叫做延迟触发

4. 边沿触发的触发器 (Edge-Triggered)

仅在CLK为上升/下降沿时输出会改变,考察上升/下降沿的一瞬间

分类

1.用两个电平触发D触发器组成的边沿触发器

三角表示上升沿触发,其左侧加圆圈表示下降沿触发

来一个上升沿翻转一次

题5.20

带异步复位端RD、置位端SD

复位、置位高电平有效

2.维持阻塞边沿触发器

3.利用传输延迟时间的边沿触发器

仅在CLK为下降沿时输出会改变,考察下降沿的一瞬间

JK同为1时,输出翻转;SR同为1时,输出不定

芯片

集成边沿D触发器:74LS74,CC4013

CP即CLK,上升沿触发

集成边沿JK触发器:74LS112,CC4027

74LS112为CP下降沿触发

CC4027为CP上升沿触发

逻辑功能及其描述方法

SR触发器

特性表

特性方程

状态转换图(状态图)

JK触发器

特性表

特性方程

状态转换图

D触发器

特性表

特性方程

状态转换图

T和T'触发器

特性表

T=1时,成为T'触发器

0保持1翻转

特性方程

JK接了同一个

状态转换图

不同逻辑功能触发器之间的相互转换

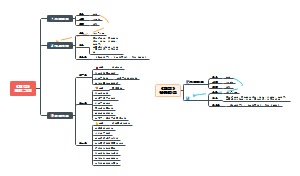

第六章:时序逻辑电路

概述

组合电路与时序电路的区别

时序电路也称状态机,State Machine

时序逻辑电路的分类

按动作特点

同步:所有触发器状态的变化都是在同一时钟信号操作下同时发生

CLK都是一个

异步:触发器状态的变化不是同时发生

CLK不是一个

按输出特点

米利(Mealy)型

输出取决于存储电路的状态、输入变量

穆尔(Moore)型

输出仅取决于存储电路的状态

可看作米利型的特例

时序逻辑电路的功能描述方法

逻辑方程组

特性方程

驱动方程

时钟方程

状态方程

输出方程

状态表

图

卡诺图

状态图

时序图

逻辑图

时序逻辑电路的分析方法

分析步骤

1. 电路图

几个触发器

有无输入输出

同步异步

2. 时钟方程、驱动方程、输出方程

时钟方程

仅异步(多个CLK)需要

驱动方程

J1=...,K1=...(看图上接线)

输出方程

Y=...

3. 状态方程

将触发器的特性方程代入驱动方程,得到状态方程

Q1*=...,Q2*=...

4. 状态表、状态图

现态->次态

箭头上方:表示输出

5. 时序图

6. 判断逻辑功能,检查自启动

同步七进制加法计数器,能自启动

若没有无效状态,则不存在自启动

几个概念

若干常用的时序逻辑电路

寄存器和移位寄存器

寄存器

由具有存储功能的触发器组合起来构成,用来存放二进制数据或代码

步骤

清零

送数

保持

例

移位寄存器

例:单向移位寄存器

来一个clk右移一位,共需4个

双向移位寄存器

74LS194

DIR:数据输入右(右移数据的输入端)

DIL:左移数据的输入端

应用

计数器

能够记忆输入脉冲个数的电路

分类

触发器是否同时翻转

同步(同一个CLK)

二进制

加法

减法

可逆

十进制

N进制

异步

数字增减

加法

减法

可逆

容量

二进制

十进制

N进制

器件实例

"16"

74LS160

十进制,0000~1001(0~9,8421码)

异步清零,同步置数

例

十进制,故1001后是0000

74LS161

4位同步二进制

16进制(即4位二进制,即模16),0000~1111

VCC:接5V

EP、ET:工作状态控制端

RD':异步复位端

D0~D4:数据输入端

LD':预置数控制端

C:进位输出端

进位时输出1

同步置数(置数要CLK控制),异步清零(清零不需要CLK控制)

“计数”:计来的脉冲的数目

74LS163

16进制(4位二进制),0000~1111

同步置数,同步清零

"19"

74LS191

单脉冲

4位同步十六进制可逆

“可逆”:可加可减

S':使能控制端

置1起到保持作用

U'/D:加法/减法控制端

置0时做加法计数

置1时做减法计数

C/B:进位/借位信号输出端,也称最大/最小输出端

加法计数,1111时,C/B置1,有进位输出

减法计数,0000时,C/B置1,有借位输出

CLK0:串行时钟输出端

当C/B=1时,在下一个CLK1上升沿到达前,CLK0端有一个负脉冲输出

CLK1:时钟输入信号

无清零功能

异步置数

加法计数:CLK1来一个脉冲进一位,如0000->0001

74LS193

双时钟十六进制加/减计数器

异步置数,异步清零

双时钟

CLKU:加计数脉冲

CLKD:减计数脉冲

RD清零端

74LS190

十进制,单时钟,可逆

与190类似,差别在进制

"29"

74LS290

异步二-五-十进制计数器

S9(0)、S9(1):置9端

R9(0)、R9(1):清0端

同时为1时清零

异步清零,异步置9

例:十进制接线

例

置零法构成六进制

0110时,清0

0110为过渡态,考虑进制时不算

法一:几个实箭头就是几进制

实箭头代表CLK脉冲来临

法二:几个状态就是几进制

过渡态不算

如0000~1001共十个状态就是十进制

置9法构成六进制

十进制,故1001后是0000

注:不可将输出端相互短路(线与)

同步计数器

异步计数器

3位异步二进制加/减法计数器

任意进制计数器的构成方法

置零法(复位法)/置数法(置位法)

N进制计数器构成M进制计数器

M<N

一片N进制即可实现

例:74LS160

异步清零,同步置数

置零法

当Q3Q2Q1Q0=0110时,RD'=0

置数法

当Q3Q2Q1Q0=0101时,LD'=0

当Q3Q2Q1Q0=0101时,LD'=0

M>N

需用多片N进制计数器

M可分解为N1*N2(N1,N2<N)

串行进位

低位片的进位信号作为高位片的时钟输入信号

左边进位时,右边才得到一个脉冲

并行进位

以低位片的进位信号作为高位片的工作状态控制信号

10*10=100

左边进位时,右边才计数一次(EP=ET=1才计数)

100进制

M不可分解(素数)

整体置零

异步清零,即左9直接清零无需脉冲

整体置数

同步置数,即左8再来一个脉冲置数

29进制

时序逻辑电路的设计方法

带有进位输出端的十三进制计数器

1. 建立原始状态图

该电路不需输入端,有进位输出用C表示,规定有进位输出时C=1,无进位输出时C=0。

不要写S0,写0000

用0001代表S0也可,但对应下角标0000更好看

2. 状态分配(状态表)

因为23<13<24,因此取触发器位数n=4(4位2进制)

3. 状态化简(卡诺图),次态方程

法一:卡诺图得最简,观察状态方程

由卡诺图得状态方程

比较JK触发器的特性方程

Q*=JQ′+K′Q

得到驱动方程

J3=Q2Q1Q0

K3=Q2'

法二:卡诺图每八个可圈,直接得驱动方程

X圈了,说明这个无关项引入了

4. 画电路图

5. 画状态转换图,检查自启动性

从图上任一状态开始,能进入有效循环,则能自启动

串行数据检测器 (P314 例6.4.2)

连续输入3个或3个以上的1时输出为1;其他输入情况下输出为0

1.状态图

2.状态表

3.卡诺图,状态方程,驱动方程

4.逻辑图

5.检查自启动

如不能自启动,想办法将无效状态引入有效循环

如11,建议引入10而不是00,这样只需要改变一个状态方程

再从头重新列状态表,只需列变了的就可以

例6.4.4,例6.4.5