导图社区 半导体制造工艺

- 30

- 1

- 0

- 举报

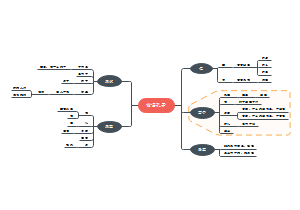

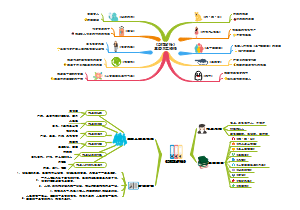

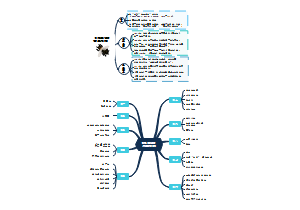

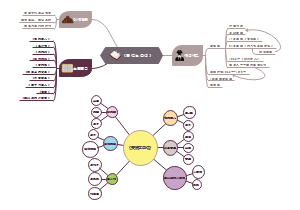

半导体制造工艺

这是一篇关于半导体制造工艺的思维导图,主要内容包括:半导体制造23个核心工艺流程,涵盖每个步骤的目的、操作细节、关键参数、设备材料及质量控制标准:,一.拉硅棒(单晶生长),二:滚磨(硅棒加工),三:切片(硅棒切割为硅片),四:倒角(硅片边缘处理),五:CMP研磨(化学机械平坦化),六:晶圆检测,七:抛光清洗(超净清洗),八:氧化(生长SiO₂薄膜)。

编辑于2025-08-31 10:09:25- 半导体工艺

- 设备材料

- 操作细节

- 关键参数

- 相似推荐

- 大纲

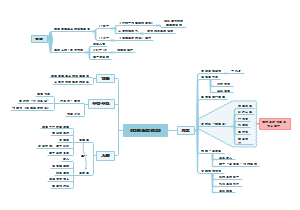

半导体制造工艺

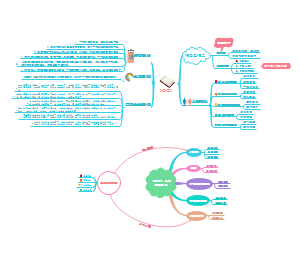

半导体制造23个核心工艺流程,涵盖每个步骤的目的、操作细节、关键参数、设备材料及质量控制标准:

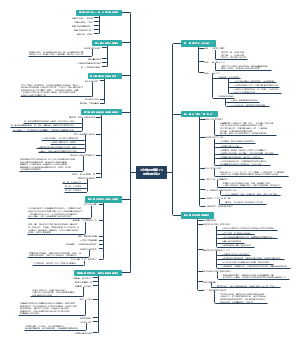

一.拉硅棒(单晶生长)

目的:将高纯度多晶硅熔融后生长出具有完整晶格的单晶硅棒(直径300mm/450mm),控制晶向(如、)。

详细步骤:

1.原料准备:

-多晶硅料(纯度99.9999999%,9N)破碎成5-20mm颗粒,清洗去除表面金属杂质(用HF+HNO₃混合液浸泡10分钟)。

-石英坩埚(纯度99.999%)内壁喷涂氮化硅(Si₃N₄)涂层(厚度5-10μm),防止硅熔体与坩埚反应生成杂质。

2.熔融阶段:

- 坩埚装入单晶炉,抽真空至1×10⁻⁵Pa,通入高纯氩气(纯度99.9999%)作为保护气,流量控制在20-50L/min。

- 射频加热或电阻加热至1410±0.1℃(硅熔点),硅料完全熔融(熔融时间约2-4小时,根据硅棒尺寸调整)。

3.籽晶处理与引晶:

- 籽晶(单晶硅棒切片,直径5-10mm,长度100-200mm)需经X射线定向,确保晶向偏差

- 籽晶下降接触熔硅表面(接触压力5-10g),保持温度稳定(±0.05℃),籽晶旋转速度5-10rpm,坩埚反向旋转3-8rpm,形成初始单晶核。

缩颈生长:

- 提升籽晶提拉速度至20-50mm/min,使晶体直径缩小至2-5mm(细颈长度50-100mm),目的是消除籽晶原有缺陷(如位错)。

放肩与等径生长:

- 放肩:降低提拉速度至0.5-2mm/min,提高温度5-10℃,使晶体直径扩大至目标尺寸(如300mm),控制直径偏差

- 等径:通过红外直径检测仪实时监控,调整温度(±0.01℃)和提拉速度(1-3mm/min),保持直径稳定,生长长度可达1.5-2m(12英寸硅棒)。

收尾与冷却:

- 提升提拉速度至5-10mm/min,降低温度,使晶体直径逐渐缩小至5-10mm,避免应力导致的晶格缺陷。

- 硅棒脱离熔硅后,在炉内以5-10℃/min的速率冷却至200℃以下(约10-12小时),防止热冲击开裂。

设备:日本Ferrotec单晶炉(型号CZ-300)、X射线定向仪(Bede D1)。

质量控制:通过红外探伤检测位错密度(要求100μs(用于功率器件需>500μs)。

二:滚磨(硅棒加工)

目的:将硅棒外圆加工至精确直径,磨出定向槽/面,确保后续切片精度。

详细步骤:

截断:

- 用金刚石砂轮切割机(刀片厚度0.3-0.5mm)切除硅棒两端的细颈和收尾部分(非有效区域),切口平面与硅棒轴线垂直度偏差

外径研磨:

- 采用无心磨床(如日本冈本OGM-300),砂轮粒度800#-1200#,冷却液为水基切削液(含0.5%纳米Al₂O₃颗粒)。

- 研磨后直径精度控制在300±0.05mm(12英寸),圆度误差

定向与开槽:

- X射线定向仪检测硅棒晶向,调整硅棒角度使目标晶向(如)与基准面偏差

- 用金刚石砂轮在硅棒表面磨出定向槽:槽宽0.5-1mm,深度0.2-0.3mm,槽长贯穿有效区域,用于后续光刻对准。

设备:德国勇克(Junker)无心磨床、东京精密定向槽研磨机。

质量控制:激光测径仪检测直径均匀性,三坐标测量仪验证定向槽位置精度(偏差

三:切片(硅棒切割为硅片)

目的:将硅棒切割为厚度均匀的薄片(硅晶圆),控制损伤层深度。

详细步骤:

粘棒:

- 硅棒用环氧树脂(如3M Scotch-Weld)粘结在玻璃基板上,粘结面平整度

- 12英寸硅棒通常3-4根并排粘结,提高切割效率。

金刚石线切割:

- 金刚石线参数:线径50-70μm(12英寸硅片),表面电镀金刚石颗粒(粒径3-5μm),线张力25-35N,线速度1200-1500m/min。

- 切割参数:工作台进给速度0.3-0.8mm/min,切割缝宽=线径+2×磨粒突出量(约70-90μm)。

- 冷却液:水基溶液(含0.1%非离子表面活性剂),流量5-10L/min,压力0.2MPa,用于降温(控制硅片温度

切割后状态:

- 单根12英寸硅棒可切割约2000片硅片,厚度300-775μm(根据应用调整),厚度偏差

- 表面损伤层深度5-10μm(由磨削应力导致的晶格缺陷层)。

设备:日本Disco DFD651切割机、中国高测股份GCT-X300。

质量控制:激光干涉仪检测TTV(总厚度偏差)10μm的划痕)。

四:倒角(硅片边缘处理)

目的:将硅片边缘(棱角)磨成圆弧或斜面,防止边缘崩裂、减少应力集中,便于后续清洗和薄膜沉积。

详细步骤:

定位:

- 硅片放入真空吸盘,通过边缘传感器对准定向槽,确保倒角位置与晶向匹配。

倒角研磨:

- 采用金刚石砂轮(粒度1000#-2000#),砂轮转速3000-5000rpm,硅片转速50-100rpm。

- 倒角形状:通常为“双圆角”(边缘顶部和底部均倒圆),圆角半径0.3-0.5mm(12英寸硅片),角度控制在45°±2°。

- 冷却液:含0.2%碳化硅(SiC)颗粒的水基液,流量2-3L/min,防止研磨热损伤。

设备:日本SpeedFam倒角机、中国盛美半导体ACM-300。

质量控制:轮廓仪检测倒角尺寸(偏差

五:CMP研磨(化学机械平坦化)

目的:通过化学腐蚀与机械研磨结合,去除切片后的表面损伤层,实现纳米级平坦化。

详细步骤:

粗抛(去除损伤层):

- 研磨垫:聚氨酯材质(硬度80 Shore A),表面开沟槽(宽0.5mm,深0.2mm)。

- 浆料:含50nm Al₂O₃颗粒的碱性溶液(pH=10),浓度10-15wt%,流量100-200ml/min。

- 参数:研磨压力30-50kPa,平台转速60-80rpm,硅片转速55-75rpm,去除量10-20μm(将损伤层完全去除)。

精抛(原子级平坦化):

- 研磨垫:软质发泡聚氨酯(硬度60 Shore A),表面多孔结构。

- 浆料:含10-20nm SiO₂颗粒的酸性溶液(pH=4-5),添加H₂O₂作为氧化剂,浓度5-8wt%。

- 参数:压力10-20kPa,转速40-60rpm,去除量0.5-1μm,表面粗糙度Ra

设备:应用材料Mirra Mesa CMP系统、Lam Research Coral。

质量控制:激光干涉仪测TTV0.5nm的凸起)。

六:晶圆检测

目的:筛选合格硅片,剔除存在表面缺陷、厚度偏差或电学性能不达标的晶圆。 详细检测项:

几何参数检测:

- 厚度:激光测厚仪(精度±0.1μm),检测点≥200个/片,确保厚度均匀性

- 翘曲度(Warp):采用激光扫描,12英寸硅片要求

表面缺陷检测:

- 光学检测设备(如KLA Tencor 2800):检测划痕(>5μm)、颗粒(>0.2μm)、凹坑,每片允许颗粒数

- 暗场显微镜:检查边缘崩边(>3μm即判废)。 3. **电学性能检测**: - 四探针测试仪:测电阻率(如0.001-100Ω·cm,根据掺杂类型调整),均匀性

- 少子寿命测试仪:微波光电导衰减法(μ-PCD),要求>50μs(逻辑芯片)或>100μs(存储芯片)。

设备:KLA Tencor SP1缺陷检测系统、Semilab WT-2000电阻率测试仪。

质量标准:合格率需≥90%(12英寸硅片),缺陷密度

七:抛光清洗(超净清洗)

目的:去除硅片表面残留的CMP浆料、金属离子、有机污染物,达到“原子级洁净”。

详细步骤:

1.预清洗:

- 兆声波清洗(频率800kHz):用去离子水(DIW)冲洗,功率50-100W,去除表面松散颗粒(30秒)。

化学清洗(RCA清洗):

- SC1清洗:NH₄OH:H₂O₂:H₂O=1:1:5(体积比),温度75-80℃,浸泡10分钟,去除有机污染物和颗粒(通过羟基化作用使颗粒脱离)。

- SC2清洗:HCl:H₂O₂:H₂O=1:1:6,温度70-75℃,浸泡10分钟,去除金属离子(如Fe、Cu、Ni,残留量

- 稀释HF(DHF)清洗:HF:H₂O=1:50,室温浸泡30秒,去除自然氧化层(SiO₂),露出新鲜硅表面。

终清洗与干燥:

- 超纯水(UPW,电阻率18.2MΩ·cm)冲洗:流量5L/min,时间5分钟,确保化学残留

- 干燥:氮气吹干(纯度99.9999%,压力0.1MPa)或离心干燥(转速1500rpm,2分钟),避免水渍残留。

设备:日本DNS清洗机、中国至纯科技湿法清洗系统。

质量控制;总有机碳(TOC)检测

八:氧化(生长SiO₂薄膜)

目的:在硅片表面生成二氧化硅(SiO₂),作为栅介质、隔离层或掩膜层。

详细步骤:

炉管准备:

- 石英炉管(纯度99.999%)在1200℃下通O₂烘烤2小时,去除内壁杂质;真空度抽至1×10⁻⁴Pa。

氧化工艺:

- 干氧氧化(用于栅氧化层):

- 通入高纯O₂(纯度99.9999%),流量2-5L/min,温度900-1000℃,生长厚度1-50nm(生长速率约0.1nm/min,遵循抛物线规律)。

- 特点:氧化层致密(密度2.2g/cm³),击穿场强>10MV/cm。

- 湿氧氧化(用于隔离层):

- 通入O₂+水蒸气(H₂O分压50-80%),温度1000-1200℃,生长厚度50-1000nm(速率是干氧的3-5倍)。

- 特点:厚度大但密度略低(2.1g/cm³),用于场氧化层。 3. **冷却**:

- 氧化结束后,关闭加热,继续通O₂至温度降至500℃以下(约1小时),防止热应力导致氧化层开裂。

设备:东京电子TEL-8000氧化炉、ASML Oxide Furnace。

质量控制:椭偏仪测厚度(偏差

九:涂光刻胶

目的:在晶圆表面涂覆均匀的光刻胶薄膜,作为光刻图案的“转移介质”。

详细步骤:

1.预处理:

- 晶圆在真空吸盘上加热至90℃(30秒),去除表面水汽;通入六甲基二硅胺(HMDS)蒸气(温度150℃),增强光刻胶与晶圆的附着力(HMDS形成硅氧烷键)。

2.光刻胶选择:

- 正胶(如AZ 1500):曝光后溶于显影液,用于高精度图形(线宽5μm

3.旋涂工艺:

- 滴胶:光刻胶(粘度50-500cP)滴在晶圆中心(量5-10ml,根据晶圆尺寸调整)。

- 低速匀胶:500-1000rpm,5秒,使胶液均匀覆盖表面。

- 高速甩胶:3000-6000rpm,30秒,通过离心力控制厚度(转速与厚度成反比:3000rpm对应1μm,6000rpm对应0.5μm)。

4.前烘:

- 热板加热至90-110℃,30-60秒,去除光刻胶中30-50%的溶剂(溶剂残留量

设备:东京电子TEL Clean Track、ASML Litho Track。

质量控制:台阶仪测胶厚均匀性

十:光刻(图案转移)

目的:通过曝光将掩膜版上的电路图案转移到光刻胶上,精度决定芯片最小线宽。

详细步骤:

掩膜版准备:

- 石英掩膜版(厚度6.35mm),镀铬图形层(厚度100-200nm),图形精度

曝光系统与参数:

- DUV光刻(28nm-130nm制程):

- 光源:ArF激光(193nm),NA(数值孔径)0.93,曝光剂量20-50mJ/cm²。 - 浸没式技术:晶圆与物镜间充水(折射率1.44),提升分辨率(分辨率=kλ/NA,k=0.35)。

- EUV光刻(

- 光源:13.5nm极紫外光(由Sn靶激光等离子体产生),功率>500W,NA 0.55,曝光剂量120-200mJ/cm²。

- 多层膜反射镜:Mo/Si多层膜(30-50层),反射率>70%(EUV无法透过透镜,需反射成像)。

套刻曝光:

- 晶圆通过光刻机的对准系统(激光干涉仪+标记识别)与掩膜版对准,套刻精度

- 分步重复曝光:每曝光一个芯片单元(die),晶圆移动至下一个单元,12英寸晶圆可包含>100个die。

设备:ASML NXE:3600B(EUV)、NXT:1980Di(ArF浸没式)。

质量控制:CD-SEM(临界尺寸扫描电镜)测线宽(偏差

十一:显影(光刻胶图案成型)

目的:去除曝光或未曝光的光刻胶,使掩膜图案在晶圆表面显影出来。

详细步骤:

显影液选择:

- 正胶显影液:2.38wt%四甲基氢氧化铵(TMAH)水溶液(碱性,pH=12.5)

- 负胶显影液:二甲苯(有机溶剂),需后续用异丙醇清洗。

显影工艺:

- 喷雾显影:显影液以0.2MPa压力喷雾到晶圆表面,时间30-60秒(根据胶厚调整),温度23±1℃。

- puddle显影:晶圆表面形成显影液液膜(厚度1-2mm),静置45秒,增强图形侧壁陡度。

冲洗与干燥:

- 超纯水冲洗30秒,去除残留显影液;氮气吹干(避免水渍污染图形)。

设备:东京电子TEL显影模块、KLA Tencor显影系统。

质量控制:光学显微镜检查图形完整性(无断线、桥连),CD-SEM测显影后线宽(与目标偏差

十二:刻蚀(图案转移至晶圆表面)

目的:去除未被光刻胶保护的晶圆表面材料(如SiO₂、Si、金属),将光刻胶图案转移到晶圆上。

详细步骤:

干法刻蚀(主流工艺):

- **等离子体刻蚀**:

- 刻蚀腔抽真空至10-100mTorr,通入刻蚀气体(如刻蚀SiO₂用CF₄+CHF₃,刻蚀Si用Cl₂+BCl₃)。

- 射频电源(13.56MHz)激发气体产生等离子体(电子温度1-3eV),离子轰击晶圆表面,与材料反应生成挥发性产物(如SiF₄)被真空泵抽走。

- 参数控制:

- 刻蚀速率:SiO₂约100nm/min,Si约50nm/min,需匹配光刻胶厚度(防止胶被刻穿)。

- 选择性:刻蚀目标材料与光刻胶的速率比>20:1(如刻SiO₂时,光刻胶刻蚀速率

- 各向异性:通过调整偏压(50-200V)控制离子轰击方向,使刻蚀图形侧壁垂直度>85°。

湿法刻蚀(辅助工艺):

- 用于各向同性刻蚀(如Si凹槽):HNA溶液(HF:HNO₃:醋酸=1:3:10),室温下刻蚀速率5-10μm/min。

设备:Lam Research Kiyo刻蚀机、中微公司Primo D-RIE。

质量控制:台阶仪测刻蚀深度(偏差十三:去胶(去除残留光刻胶)

目的:刻蚀完成后去除剩余光刻胶,避免影响后续工艺(如掺杂、薄膜沉积)。

详细步骤:

等离子体灰化(干法去胶):

- 去胶腔通入O₂(流量500sccm),射频功率300-500W,产生氧等离子体(O*自由基)。

- 光刻胶(有机聚合物)与O*反应生成CO₂和H₂O,被抽走,去胶速率1-2μm/min,时间5-10分钟。

- 优点:无液体残留,适用于精细图形。

湿法去胶(辅助):

- 硫酸+双氧水(H₂SO₄:H₂O₂=3:1),温度120℃,浸泡10分钟,溶解光刻胶残留物。

- 用于干法去胶后的收尾,去除金属杂质(如Cu、Fe)。

设备:东京电子TEL Ashing系统、盛美半导体湿法去胶机。

质量控制:X射线光电子能谱(XPS)检测表面碳含量(

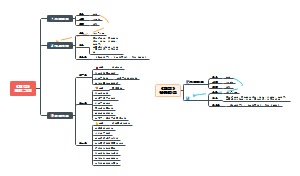

十四:离子注入(掺杂)

目的:将杂质离子(如B、P、As)注入硅晶格,改变半导体电学性能(形成N型或P型区域)。

详细步骤:

离子源制备:

- 固体源:B₂O₃加热产生B离子,P₄O₁₀产生P离子;气体源:AsH₃分解产生As离子。

- 离子经电场加速、磁场筛选(质谱分析),获得单一荷质比的离子束(如B⁺、P⁺)。

注入参数:

-能量:1keV-1MeV(低能量注入浅结,如源漏扩展区;高能量注入深结,如阱区)。

-剂量:1×10¹¹-1×10¹⁶ atoms/cm²(剂量决定掺杂浓度)。

-角度:7°倾斜注入,避免离子沿硅晶格沟道深入(减少深度偏差)。

掩膜保护:

- 用SiO₂或光刻胶作为掩膜(厚度根据注入能量计算,如1MeV P⁺需SiO₂掩膜厚度>1μm),未保护区域接受离子注入。

设备:应用材料Quantum X注入机、Axcelis Purion H系列。

质量控制:二次离子质谱(SIMS)测掺杂深度(偏差

十五: 退火(激活杂质与修复损伤)

目的:通过高温处理激活注入的杂质离子(使其电离导电),修复离子注入导致的晶格损伤。

详细步骤:

快速热退火(RTA,主流工艺):

- 晶圆放入RTA腔,通入N₂保护气(流量20L/min),避免氧化。

- 红外灯加热至900-1100℃(升温速率50-100℃/s),保温10-60秒(根据结深调整)。

- 优点:热预算低(减少杂质扩散),适合浅结(

炉管退火(辅助工艺):

- 适用于深结激活:温度800-900℃,保温30-60分钟,N₂氛围,升温速率5℃/min。

效果:

- 杂质激活率>90%(如P离子激活后电离为P⁺),晶格损伤修复率>95%(位错密度

设备:应用材料Centura RTA、东京电子TEL RTA系统。

质量控制:少子寿命测试(激活后需恢复至注入前的80%以上),霍尔效应仪测载流子浓度(偏差

十六: 薄膜沉积(生长功能薄膜)

目的:在晶圆表面沉积各类薄膜(如多晶硅、SiN、金属、高k介质),用于栅极、介质层、互连等。

详细工艺:

LPCVD(低压化学气相沉积):

- 用于沉积多晶硅、Si₃N₄:

- 多晶硅:SiH₄气体,温度600-650℃,压力100-500mTorr,沉积速率10-20nm/min,厚度均匀性

- Si₃N₄:SiH₂Cl₂+NH₃,温度750-850℃,用作掩膜或钝化层,应力控制在100-300MPa。

PECVD(等离子体增强CVD):

- 低温沉积(

- SiO₂:SiH₄+O₂,射频功率500W,沉积速率50-100nm/min,用于层间介质(ILD)。

- 低k介质(SiCOH):Si(CH₃)₄+O₂,k值2.5-3.0,用于减少互连RC延迟。 3.ALD(原子层沉积):

- 原子级控制:如Al₂O₃沉积,交替通入Al(CH₃)₃和H₂O,每循环生长0.1nm,厚度偏差

- 用于高k栅介质(如HfO₂,k=25),替代传统SiO₂(k=3.9),降低栅漏电。

设备:应用材料Endura PVD系统、Lam Research Versa系统。

质量控制:椭偏仪测薄膜厚度,X射线衍射(XRD)分析结晶度,应力仪测薄膜应力(避免晶圆翘曲)。

十七: 金属化(制备导电互连)

目的:沉积金属层(主要是铜),形成芯片内部的导电通路(互连线),连接晶体管与外部引脚。

详细步骤:

大马士革工艺(铜互连主流技术):

- 沟槽刻蚀:等离子体刻蚀层间介质(低k材料),形成互连线沟槽(线宽5-50nm)和通孔(直径10-30nm)。

-阻挡层沉积:PVD(物理气相沉积)沉积Ta/TaN(厚度5-10nm),防止铜扩散到硅或介质中。

-铜籽晶层:PVD沉积10-20nm铜籽晶,作为后续电镀的导电层。

-电镀铜:酸性硫酸铜溶液(CuSO₄+H₂SO₄),电流密度10-30mA/cm²,填充沟槽和通孔(无空洞),电镀速率100-200nm/min。

铜CMP:

- 去除表面多余铜,保留沟槽内的铜作为互连线,表面粗糙度Ra

金属层结构:

- 先进制程(如3nm)包含10-12层金属互连,最上层为铝垫(用于键合),厚度1-2μm。

设备:应用材料SABRE电镀系统、Lam Research铜CMP机。

质量控制:SEM检查铜填充完整性(无空洞、缝隙),四探针测线电阻(偏差

十八:晶圆减薄(背面减薄)

目的:减小晶圆厚度(从775μm减至50-200μm),便于后续切割划片,降低封装后的芯片厚度(适应轻薄化需求)。

详细步骤:

正面保护:

-晶圆正面贴UV固化膜(厚度50-100μm),防止减薄过程中划伤电路图案。

减薄工艺:

-粗磨:金刚石砂轮(粒度320#),去除70-80%厚度(如从775μm减至200μm),压力50-100kPa,转速3000rpm。

-精磨:砂轮粒度1200#,减至目标厚度+10μm,表面粗糙度Ra

-化学蚀刻(可选):用HF+HNO₃溶液去除10μm,消除研磨损伤层。

背面处理:

- 去除UV膜(紫外光照射30秒,胶带粘性降低),背面清洗(SC1+SC2)。 **设备**:日本Disco DGP8760减薄机、中国宇环数控YH2M8140。

质量控制:激光测厚仪检测厚度均匀性(十九:切割划片(晶圆分离为芯片)

目的:将晶圆沿切割道(Saw Street)分离为单个芯片(Die),切割道宽50-100μm,内无电路。

详细步骤:

1.划片前准备:

- 晶圆背面贴蓝膜(粘性50-100g/cm),固定在框架上(防止切割后芯片散落),蓝膜需耐高温(>80℃)。

切割工艺:

- 刀片切割(主流):

- 金刚石刀片(厚度20-50μm,粒度3000#),转速30000-40000rpm,进给速度50-200mm/s。

- 切割深度:超过晶圆厚度5-10μm(确保完全分离),冷却液(水基)流量50ml/min,降温防损伤。

- 激光切割(先进工艺):

- 紫外激光(355nm),脉冲能量10-50μJ,通过烧蚀切割道材料实现分离,无机械应力,适合薄晶圆(

设备:Disco DAD3350刀片切割机、Coherent激光划片机。

质量控制:光学检查芯片边缘(无崩边>10μm),芯片尺寸偏差

二十:晶圆贴片(芯片固定)

目的:将单个芯片从蓝膜上转移至封装基板或引线框架,确保固定牢固。

详细步骤:

芯片拾取:

- 自动固晶机的吸嘴(直径0.5-2mm,根据芯片尺寸选择)通过负压(-50kPa)拾取芯片,视觉定位(精度±1μm)。

贴片工艺:

- 基板或引线框架预热至80-120℃,涂覆导电胶(银浆,用于功率器件)或绝缘胶(环氧树脂,用于逻辑芯片),胶厚10-30μm。

- 芯片对准基板焊盘(偏差

固化:

- 烘箱加热至150-180℃,固化30-60分钟,胶层剪切强度>50MPa(确保芯片不脱落)。

设备:ASM AD860固晶机、K&S IConn贴片系统。

质量控制:X射线检查贴片对准精度,推力测试(>50g)验证粘结强度。

二十一:引线键合(芯片与基板互连)

目的:用金属线(金、铜)连接芯片的焊盘(Pad)与基板的引脚(Lead),实现电学导通。

详细步骤:

键合线选择:

- 金线:直径15-50μm(纯度99.99%),导电性好(电阻率2.4μΩ·cm),适合高频器件。

- 铜线:直径15-50μm(纯度99.99%),成本低(约为金的1/10),电阻率1.7μΩ·cm,需氮气保护防氧化。

热超声键合(主流工艺):

- 第一键合(球键合):

- 键合机的毛细管(直径50-100μm)末端放电(电火花),将线端熔成金球(直径为线径的2-3倍)

- 金球压在芯片焊盘上,施加超声振动(频率60-120kHz)和压力(50-200g),温度150-200℃,形成欧姆接触。

- 第二键合(楔键合):

- 金线拉至基板引脚,毛细管施加压力和超声,形成楔形键合,线弧高度50-200μm(避免线弧过低短路)。

设备:K&S Maxum Ultra键合机、ASM AB559A。

质量控制:拉力测试(金线>5g,铜线>8g),键合点直径(为线径的1.5-2倍),无虚焊(通过X射线检测)。

二十二:封装(芯片保护与散热)

目的:用封装材料包裹芯片,保护其免受环境影响(湿度、机械应力),同时提供散热通道。

详细工艺:

封装类型与工艺:

- 传统封装(DIP/QFP):

- 模具注塑:环氧树脂(如Sumitomo EME-G700)注入模具,包裹芯片和引线,注塑压力50-100bar,温度175℃/60秒固化。

- 先进封装(BGA/SiP):

- 底部填充:芯片与基板间隙注入环氧树脂(CTE 15-20ppm/℃),烘烤固化(150℃/30分钟),防止焊点疲劳。

- 倒装芯片封装:焊球回流焊(230-260℃,氮气氛围),形成机械和电学连接,焊球直径50-200μm,间距100-500μm。

后固化与去飞边:

- 烘箱175℃/4小时后固化,提升封装体强度(抗弯强度>150MPa)。

- 激光或机械打磨去除封装体边缘飞边(毛刺

设备:ASM塑封机、日东精工底部填充设备。

质量控制:X射线检测焊点空洞率(

二十三:测试(筛选合格芯片)

目的:通过电学测试验证芯片功能、性能和可靠性,剔除失效产品。

详细步骤:

晶圆级测试(CP,Chip Probe):

- 探针台(如Cascade Microtech Summit 12000)的探针卡(探针直径20-50μm)接触晶圆上的测试焊盘。

- 测试参数:直流参数(电压、电流、电阻)、交流参数(频率、延迟),筛选出功能失效的芯片(做标记)。

成品测试(FT,Final Test):

- 封装后的芯片放入自动测试设备(ATE,如泰克UltraFLEX),测试项包括: - 功能测试:验证逻辑运算、存储读写等核心功能。

- 性能测试:速度(如CPU主频)、功耗(待机电流

- 可靠性测试:高温工作(HTOL,125℃/1000小时)、温度循环(-40℃至125℃/1000次)、静电测试(ESD,±2kV)。

分选与标记:

- 合格芯片按性能分级(如商业级、工业级、车规级),激光标记(二维码+型号),不良品标记“NG”。

设备:泰克ATE测试系统、东京精密探针台。

质量控制:最终良率≥90%(车规级要求≥99.9%),可靠性测试失效数