导图社区 数字电路

- 814

- 64

- 12

- 举报

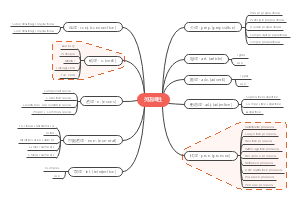

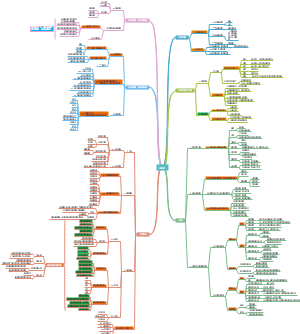

数字电路

基于天津大学测控专业数电课程资料,包括1.逻辑代数、2.Verilog、3.逻辑门、4.组合逻辑电路、5.锁存触发、6.时序电路、7.存储器、8.脉冲发生、9.ADDA等的概念与公式。

编辑于2021-07-02 16:28:21- 数电

- 数字电路

- 相似推荐

- 大纲

编码

格雷码

有权码

BCD

无权码

格雷码,余3码

逻辑运算

与非

或非

异或

同0异1

线与

高电平-低电平 短路 任何一路低,Y拉低

CMOS

同或

同1异0

定律

01律

分配律

反演律(摩根

吸收率

反函数

对偶

最小项

逻辑门电路

CMOS

12V

TTL

5V

拉电流1→ 灌电流0←

漏极开路OD门

OC门

TTL

三态门TSL

01高阻态

传输门

组合逻辑电路

1抽象

2列真值表

3表达式

4逻辑图

卡诺图

编码器

二进制编码器

十进制-二进制

普通编码器

只允许一路有效输入

优先编码器

多路优先权最高

译码器

二进制译码器

二进制-十进制

数码管

唯一地址译码器

其列代码转换为11对应有效信号

代码变换器

一种代码变另一种

锁存器

SR锁存器

D锁存器

触发器

边沿敏感

锁存器:电平敏感

RS触发器

CP。下降沿

D触发器

CP。下降沿

同步触发 受控CP

异步触发 不受控CP

存储器

位

bit

字长

字位数

地址

字在存储器位置

字数

字总量

存储容量

RAM

随机存储器

上电读写,掉电数据丢失

数据频繁读写(易失性存储器

SRAM

静态,寄存器存储

不刷新,快,集成低,功耗大

动态,电容存储

刷新,集成度高,成本低

DRAM

ROM

只读存储器

工作状态只可读,掉电不丢失

存放固定信息(程序,常数(非易失性存储器

固定ROM

可编程ROM

PROM

EPROM

E²ROM

时序逻辑电路

同步

统一时钟信号,CP下才转换

异步

各触发器状态转换不同步

米利

输入&存储 决定输出

摩尔

存储决定输出

分析

1逻辑方程组

激励

状态

输出

2状态表

3状态图

寄存器

存储二进制数

1触发器寸1位二进制数

移位寄存器

可寄存,在脉冲下移动

T计数器

T触发器

脉冲产生

单稳态

一次一脉冲,宽度固定,可调

施密特

波形变换

波形整形

消除干扰

幅度鉴别

多谐振荡器

反馈延迟环节(RC电路):RC电路充放电性质实现延时,输出电压延时后,反馈到开关器件输入端,改变输出状态->脉冲波形输出

数模

DA

分类

解码网络

T型

倒T型

权电流

不受开关导通电阻影响,精度++

模拟电子开关

CMOS

双极型

分辨率

AD

误差

4位AD VREF=5V Δ=5/16

分类

并联比较型

逐次比较型

分辨率

转换误差

实际数字量-理论数字量

Vivado

新建工程

Finish

流水灯

仿真

综合约束

约束

添加对应接口 改为3v3

添加时钟约束

将刚才的IO约束保存到新建的约束文件

在I/OPorts 保存(ctrl+s)

生成比特流

下载程序

插上fpga

比特流文件生成成功后,自动填充

烧写

Done!

代码

流水灯

module example(clk,clr,led); input clk,clr; //输入时钟信号与清除 output reg [7:0] led; //led寄存器 reg [28:0] counter; //计数 always @ (posedge clk) //当上升沿来时 begin if(!clr) //清除 begin counter <= 0; //计数清0 led <= 8'h01; //位置归1 end else //未清除时 if(counter < 50000000) //2Hz counter <= counter +1; else begin counter <= 0; //计时到达 led <= {led[6:0],led[7]};//位拼接,左移 end end endmodule

仿真

`timescale 1ns / 1ps module tb_led(); parameter DELY = 20; reg clk; reg clr; wire [7:0] led; flow_led i1( .clk (clk), .clr (clr), .led (led) ); initial begin clk=1'b0; clr=1'b0; #(DELY*2) clr=1'b1; end always begin #(DELY/2) clk=~clk; end endmodule

数电

R进制

2进制

整数

÷2取余←

小数

×2取整→

2B 8O 10D 16H

机器数

无符号数

0和正

有符号数

0正1负

原码

反码

符号位不变,逐位取反

补码

负数:反码+1

正数:=原码

BCD码

每位4位表示

某位和>9

+6修正

某位差需借位

-6修正

格雷码

抑制过度噪声

二值逻辑

代数表达式

与

或

非

与非

或非

异或

同0异1

同或

同1异0

真值表-表达式

输入输出

输出1得行标出

子主题

逻辑代数

反演率

吸收律

常用

与或表达式

一次摩根->与非-与非表达式

规则

1逻辑等式,某函数带等式两边出现的变量A

反演

先与后或

非变量外的非号不变

对偶

逻辑恒成立时对偶式成立

最小项

n个变量

任一最小项

仅1组变量取值使其=1

最小项积=0

全体最小项和=1

杨凌辉

17东配203

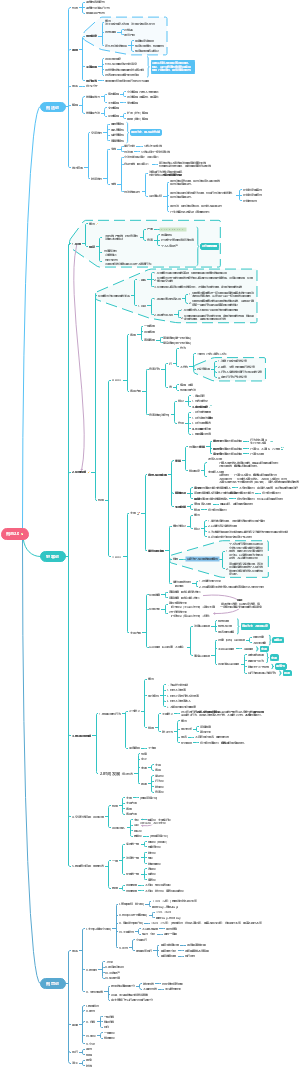

Verilog

逻辑

0

逻辑假

1

逻辑真

x

不确定

z

高阻态

常量

整数

带基数形式

<+/-><位宽>' <基数符号><数值>

实数

23_5.1e2 5E-4

字符串

“hello”

定义

parameter

parameter SEL=8, CODE=8'ha3; /*分别定义参数SEL代表常数8(10进制), 参数CODE代表常量a3(16进制)*/

变量

net

线网类型

wire

网络型变量(默认位宽1

驱动

连接到门/模块输出端

持续赋值assign

tri

wand

supply0

variable

变量类型

reg

常用的寄存器型变量(可定义位宽)

reg [n-1:0] 变量名1,变量名2,…,变量名n; 例: reg clock;//定义一个1位寄存器变量 reg [3:0] counter; //定义一个4位寄存器变量

integer

32位带符号的整数型变量

time

64位无符号的时间变量

real

64位带符号的实数型变量

realtime

必须在过程语句initial always中

运算

标量

位宽1,不指定位宽

向量

位宽>1的变量

位选择

d=a[7]&b[7];

域选择

d c=a[7:4]+b[3:0];

运算符

整除取整

运算操作数有x/z

结果x/z

逻辑比较

== !=

逻辑值比较

=== !==

按位比较

同位的x/z认为相同

位拼接

设A=1’b1,B=2’b10,C=2’b00;

则{B,C}=4’b1000; {A,B[1],C[0]}=3’b110; {A,B,C,3’b101}=8’b11000101;

{{}}

重复拼接

{4{A}}=4’b1111; {2{A},2{B},C}=8’b11101000;

缩位运算

条件

condition_expr?expr1:expr2;

行为语句

过程

initial

执行一次

always

重复执行

always @(<敏感信号表达式event-expression>) begin //过程赋值 //if-else, case, casex, casez选择语句 //while, repeat, for循环 //task, function调用 end

敏感信号

@(a) //当信号a的值发生改变 @(a or b) //当信号a或信号b的值发生改变 @(posedge clock) //当clock 的上升沿到来时 @(negedge clock)//当clock 的下降沿到来时 @(posedge clk or negedge reset) //当clk的上升沿或reset信号的下降沿到来

块

begin-end

串行顺序执行

赋值

assign

=

<=

wire a,b,c assign c=a&b

非阻塞<=

整个过程块结束才赋值

非立刻改变

无顺序

阻塞=

语句结束立即赋值

条件

if-else

else if

case

casez

casex

只对非x比较

只对非z

循环

for

initial begin for(i=0;i<4;i=i+1) out = out +1; end

while

initial begin i=0; while(i<0) i=i+1; end

forever

连续

repeat

执行n次

initial begin repeat(5) out = out +1; end

任务

task

任务调用、定义端口变量一一对应

定义调用在一个module内

子主题

函数

function

模块

module endmodule

模块名

模块名(端口1,端口2。。)

无外界信息交互,不需要端口列表

IO

input

输入端口

output

输出端口

inout

input 端口名1; //该端口是位宽为1的输入端

input [w-1:0] 端口名2; //该端口是位宽为w且w>1的输入端

output 端口名3,端口名 4; //表示位宽为1的两个输出端

output [t:1] 端口名5; //该端口是位宽为t的输出端

inout [k-1:0] 端口名6; //该端口是位宽为k且k>1的双向总线端

wire

信号数据类型

assign

逻辑功能描述

参数

wire 变量名1,变量名2; //表示位宽为1的两个线网(net)型信号

wire [w-1:0] 变量名3; //该变量表示位宽为w且w>1的线网型信号

线网型信号

描述连线,实时变化

reg 变量名4; //该变量表示位宽为1的寄存器型信号

寄存器型信号

描述寄存器,两次赋值之间不变

reg [t:1] 变量名5,变量名6; //表示两个位宽为t的寄存器型信号

parameter 参数名1=表达式1,参数名2=表达式2; //表示两个参数常量

参数

可变常量(延时/宽度

测试

module endmodule

模块名

reg

变量用于产生变化输入

wire

变量用于记录输出

Initial

初始化

aoi u1(.a(a),.b(b),.c(c),.d(d),.f(f));

调用被仿真模型

调用

位置关联方式

名称关联方式

module <模块名> (<输入输出端口列表>); output 输出端口列表; //输出端口声明 input 输入端口列表; //输入端口声明 /*定义数据, 信号的类型, 函数声明*/ wire 信号名; reg 变量名; //逻辑功能定义 assign <结果信号名>=<表达式>; //使用assign语句定义逻辑功能 always @ (<敏感信号表达式>) //用always块描述逻辑功能 begin //过程赋值 //if-else, case语句 //while, repeat, for循环语句 //task, function调用 end //调用其他模块 <被调用模块名module_name > <例化模块名> (<端口列表port_list >); //门元件例化 门元件关键字 <例化门元件名> (<端口列表port_list>); endmodule

同时执行

2个/多个always块

子主题

逻辑门

开关电路

TTL

参数

输出波动<输入波动

电流

拉电流

输出高,电流→负载

灌电流

输出低,电流←负载

扇

扇入数

输入端数

扇出数

带动同类门数量

延时

容性

电平高低伴随内部充放电

电源高

导通电阻↓ 充放电快

延迟低

功耗

负载↓、电容↓

信号频率↓

电源电压↓

功耗↓

门

漏极开路

线与

低

高

三态门

01

高阻态

组合逻辑电路

设计

数据流

行为级

竞争冒险

竞争

一个逻辑门两个输入端信号同时向相反方向变化,变化时间有差异

冒险

由竞争可能产生输出干扰脉冲

消除

消除互补变量

消除

增加乘积 避免互补相加

输出端并联电容

编码器

赋予二进制代码特定含义

普通编码器

任何时候只允许一路有效输入

优先编码器

多路有效输入,优先权最高一个编码

译码器

唯一地址译码器

系列代码转换为一一对应有效信号

二进制

2-10进制

显示译码器

子主题

数据选择器

二选一

算术

加法

串行进位加法器

超前进位加法器

输入加数与被加数时,同时获得全加进位信号

减法

补码

触发器

双稳态

同

01两个稳定状态,确定后自行保持,1锁存器/触发器储存一位二进制码

异

锁存器

电平敏感

触发器

脉冲边沿敏感

锁存器

RS锁存器

逻辑门控

D锁存器

E0

不变

E1

Q=D

触发器

上升下降沿电平敏感

D触发器

RS触发器

约束条件

S·R=0

JK触发器

T触发器

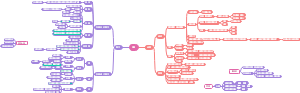

时序电路

概念

组合逻辑电路

输出取决于同一时间输入,无关 原来状态

无反馈记忆

门电路

时序逻辑电路

输出状态取决于 同一时刻输入、原来状态

有反馈记忆

组合逻辑电路+存储电路

同步时序电路

统一时钟脉冲CP

异步时序电路

无统一时钟

各触发器变化不同步

输出信号分类

米利型

输入&存储 决定输出

易受干扰

输入端抖动反馈到输出端

摩尔型

存储决定输出

描述

方程组

输入信号

输出信号

驱动存储电路→下一状态的激励信号

存储电路状态 状态信号

驱动激励方程

激励信号与输入信号、状态变量

状态方程

存储电路现态→次态

输出方程

输出信号、输入信号、当前状态变量

状态表

m位状态变量+i位输入信号

行

状态表

状态名S代替QQ

状态图

时序波形

分析电路

设计

有限状态机

对有 逻辑顺序 或 时序规律 事件的描述方法

顺序控制电路

设计

功能要求

状态图

状态编码

分段状态机主体

always描述转移条件、规律

always组合逻辑描述输出

检查是否有自启动能力

状态是否有初始、默认值

always复位赋初值

case有default

时序逻辑

寄存器

存储二进制数据

触发器构成

n位二进制 — n个触发器

74HC374

脉冲边沿触发

74HCT374

时钟电平触发

移位寄存器

寄存数码,在时钟脉冲CP 使数码 高->低移动

单向

左

右

双向

基本移位寄存器

串入

并出

串出

寄存n位二进制码

n个CP完成串行

获得并行

再n个CP串行输出

8位移位寄存器74HC/HCT164

双向移位寄存器

右

低->高

左

高->低

74HCT194

计数器

脉冲个数(T触发器

模

容量,有效状态=模数

分类

计数进制

二进制

10

n

方向

+

-

可逆

控制

同步

异步

异步二进制计数器

缺点

延时大

每个触发器延时

N位计数器最高

脉冲周期

74HC/HCT393

双4位异步二进制计数器

同步二进制计数器

状态刷新同时进行

同步刷新,都比CP滞后1

输出稳定,工作速度快

结构复杂

74LVC161

同步时序逻辑电路

分析

逻辑方程

各触发器激励方程 & 状态方程

触发器状态转换方程

输出方程

状态表

状态图

时序图

确定功能

米利型

摩尔型

混合型

修改模式

S4

增加

S1

减少

S3

编辑左移

S4

编辑右移

计时模式

计数

存储器

半导体存储器

RAM

随机存储器

上电读写,掉电数据丢失

数据频繁读写(易失性存储器

SRAM

DRAM

ROM

只读存储器

工作状态只可读,掉电不丢失

存放固定信息(程序,常数(非易失性存储器

固定ROM

可编程ROM

PROM

EPROM

E²ROM

位bit

存储信息基本单位

字长(位数

子主题

地址

字编号,存储器中的位置

字数

字总量=2^n

存储容量

字数×字长

只读存储器

不可遍程ROM

制作时固化

可编程ROM

PROM

出厂全0/1

熔丝技术改写一次

EPROM

芯片有窗口,紫外线擦除、烧写器写入

E²PROM

不同电平擦除写入,擦写万次

Flash

NAND、NOR

先擦后写

有mos存0

时钟顺序

tAA 地址存取时间

tCE 片选使能时间

tOE 输出使能时间

tOH 数据保持时间

tOZ 输出变Z时间

应用

存储器

存数据、程序

译码编码

待译码、待编码数为地址,结果为存放在该地址数据

函数发生器

变量=地址码,对应函数值为存放数据(查表

地址扩展

4×4→8×8

增加一位地址A2

与

随机存储器

RAM

SRAM

静态RAM

寄存器(锁存器结构存储信息,不必持续刷新,快速

集成度低,功耗大

DRAM

动态RAM

电容存储信息,不断刷新,否则丢失

集成度高,成本低

时序

FPGA

2维数组

SRAM

脉冲波形

单稳态触发器

只能稳定在一个状态

门电路组成

RC微分积分电路

无影响

不能

电容充电

重复触发

74121

单稳态

集成单稳态

单稳态应用

施密特触发器

电平触发器件

正向阈值电压

负向阈值电压

抗干扰性好

应用

波形变换

波形整形

消除干扰

幅度鉴别

多谐振荡

门电路组成

施密特触发器组成

串口

频率计

显示

了解施密特特征应用

计算延时

单稳电路图,分析计算,画图

二极管作用

延时脉冲时间

ADDA

DA

数字量转化为与之正比模拟量

分类

解码网络结构

T型电阻网络DAC

倒T型电阻网络

权电流

模拟电子开关

CMOS开关型

双极型开关型

电流开关型

ECL电流开关型

倒T型

流入负端总电流

n位

电路中输入的每个二进制数

均能得与之正比的模拟电压输出

输出模拟电压

导通电阻

影响电流分配精度

精度

电路参数

基准电压稳定性好

倒T型电阻网络R与2R电阻比值精度高

高位到低位按2整数倍递减,导通电阻相应按2整数倍递增

权电流

恒流源电路中

支路权电流大小不受开关导通电阻影响

降低对开关电路要求,提高转换精度

输出方式

单极性

输入

输出

双极性

输入

补码

补码对应真值

偏移码

输出

技术指标

分辨率

最小输出电压

输出电压增量

满刻度输出电压

转换精度

对给定数字量,D/A转换器实际值与理论值最大偏差

原因

各元件参数值存在误差(运放0漂,电阻差异

转换误差

比例系数误差

失调误差

系统整体漂移

非线性误差

转换时间

输出模拟电压/电流到稳定输出所需时间

手册给出

最大转换时间

输出全0→全1,输出达到稳定值所需时间

AD

取样

保持

量化

编码

采样

不同时间点把信号采样,在时间连续的模拟信号转换为时间离散信号

采样定理

采样频率>最高频率2倍

完整保留原始信号信息

合理

采样密

更反映信号变化规律

采样松

信号失真

保持

取样电路后要求采样模拟信号保持一段时间

时间离散、数值连续

量化

数值上连续信号→数值离散信号

时间离散、数值离散

最小量化单位

量化误差=真值-量化值

原理误差,无法消除

AD转换器位数越多,量化误差越小

量化方式

只舍不入

最大量化误差

四舍五入

最大量化误差

编码

AD转换器输出的数字量

直接AD转换器

不经过中间变量,输入模拟直接转换为输出

并行比较型

输入电压同时加到所有比较器输入端

转换时间最短

电路复杂

逐次反馈比较型

输出数字量位数越多,转换精度越高

完成一次转换时间,与位数n、时钟脉冲频率有关

位数越少,时钟频率越高,所需时间越短

并联

转换速度快,时间10us~1us,电路复杂

逐次

转换速度适中,时间几us~100us,转换精度高

间接AD转换器

输入模拟信号转换为中间变量(时间/频率

数字量

分辨率

能分辨模拟输入信号最小变化量

AD转换位数n,满量程电压Vm

分辨率=

参考电压

模数分离

要求

基本原理

倒T型电阻网络DA转换器

并行比较型,逐次比较型

ASIC

基本

简单可编程

GAL、PAL

CPLD

复杂可编程逻辑器件

FPGA

现场可编程门阵列

相同

功能

遍程过程

统称可编程逻辑器件PLD

不同

芯片内部原理结构

一个二维逻辑块阵列

输入/输出块

连接逻辑块的互连资源

基于乘积项的CPLD

宏单元

基本结构,实现基本逻辑工程

可编程连线

信号传递,连接所有宏

IO控制块

输入输出特性控制

现代FPGA

基本逻辑单元

Slice(切片

Xilinx

两个核心逻辑单元LC

LE(Logic Element

Atera

原理

查找表LUT

本质是RAM

判断

CPLD掉电后不丢失