导图社区 电子技术基础(数字部分)下

- 31

- 0

- 0

- 举报

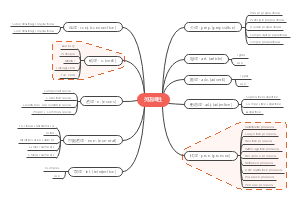

电子技术基础(数字部分)下

这是一个关于电子技术基础(数字部分)下的思维导图,涵盖半导体储存器及可编程逻辑器件、脉冲信号的产生与整形、锁存器和触发器、时序逻辑电路、二值逻辑变量与基本逻辑运算等内容。

编辑于2025-06-13 16:19:38- 电子信息

- 数电

- 时序逻辑电路

- 锁存器和触发器

- 相似推荐

- 大纲

电子技术基础(数字部分)下

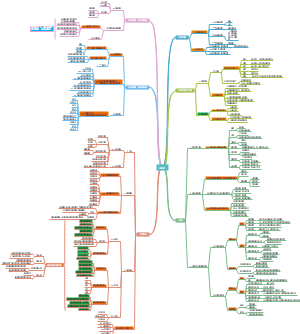

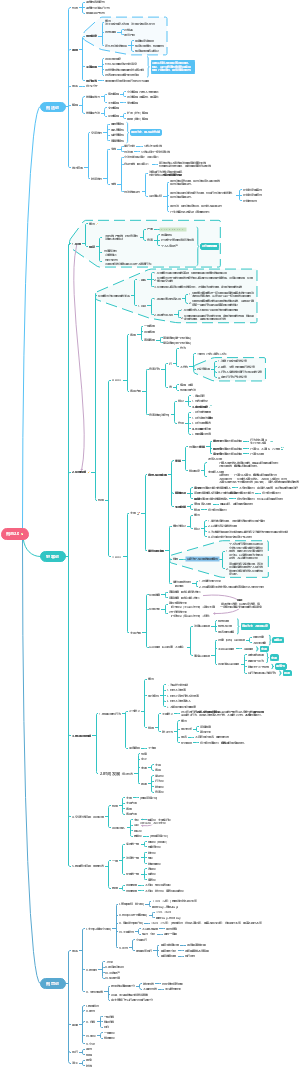

锁存器和触发器

基本双稳态电路

定义

一旦进入其中一种状态,就能保持长期不变的电路单元电路

是各种锁存器,触发器储存单元的基础

锁存器

电平触发

SR锁存器

基本SR锁存器

用或非门构成的SR锁存器

不定状态特性:可能输出全为零或全为一(需要分情况具体判断)不定状态不稳定,当输入全部取反(功能是保持原有状态)或者使能端“关闭”,就无法维持原状态而无法判断之后的状态

低电平保持

置位端输入高电平输出置位状态

复位端输入高电平输出复位状态

高电平无效

两个或非门

注意管脚位置

端口状态

Q=0,Q非=1(0状态或复位状态)

Q=1,Q非=0(1状态或置位状态)

S 置位端(置1端)

通用,SR锁存器,触发器S端输入1则Q端输出1,S非端输入0则Q端输出1,某些情况需要自己判断端口。(其他锁存器,触发器的道理相同)

R 复位端(置0端)

用与非门构成的SR锁存器

类似

两个或非门

基本SR锁存器的应用

去抖动电路

门控SR锁存器

门控SR锁存器的逻辑功能

加上一对与门和一个控制端(相当于使能端)

电平触发,不是边沿触发

注意输入R,S的正负

E输入高电平有效

加上一个圆圈则是低电平有效

用与非门构成的门控SR锁存器

D锁存器

单输入,一使能端

D锁存器的电路结构

传输门控D锁存器(透明锁存器)

使能端E,数据输入端D

当E=1,Q=D。当E=0,Q保持原来不变

逻辑门控D锁存器

加入非门以保证S,R不同时为1

逻辑功能和传输门控D锁存器完全相同

D锁存器集成电路

D锁存器的动态特性

D触发器

边沿触发

主从D触发器

由主锁存器和从锁存器组成

箭头表示电路对CP信号的脉冲边沿敏感,如果是下降沿触发,加上一个圆圈

具有清零和置数输入的主从D触发器

异步与同步清零

具有使能控制的主从D触发器

其他结构的D触发器

D触发器的动态特性

触发器的逻辑功能

边沿触发,也有对应同名电平触发器(同步触发器)

次态和现态

触发到达之前的状态称为现态,触发到达之后的状态称为次态

现态

次态

D触发器

特性表

以现态为变量,次态为函数,描述他们之间的逻辑关系的真值表

特性方程

状态转换图

每个状态用圆圈表示,箭头表示转换方向,起点表示现态,终点表示次态,箭头旁标明状态转换输入变量的取值

JK触发器

特性表

保持,置零,置一,翻转四种功能

特性方程

状态转换图

T触发器

特性表

T=0时,状态保持不变,T=1时,触发一次翻转一次

特性方程

状态转换图

SR触发器

特性表

仅有保持,置位和复位功能

特性方程

状态转换图

D触发器逻辑功能转换

D触发器构成JK触发器

构成T触发器

构成T'触发器

时序逻辑电路

时序逻辑电路的基本概念

时序逻辑电路的基本结构和分类

时序逻辑电路的基本结构

概念

输入信号(向量I)

输出信号(向量O)

激励信号(向量E)

状态信号/变量(向量S)

表示时序电路的当前状态(现态)

次态

时序逻辑电路的下一状态

时序逻辑电路的基本方程组

激励方程组

状态转换方程组

输出方程组

异步与同步时序电路

异步

不同时钟脉冲

同步

同一时钟脉冲

米利型和穆尔型时序电路

米利型

输出信号与状态变量和输入信号有关

穆尔型

输出信号仅与状态变量有关,和输入信号没有直接联系

时序逻辑电路的功能表达

逻辑方程组

激励方程组

储存电路的激励信号为函数,现态和输入信号为变量

状态转换方程组

次态为函数,激励信号和现态为变量

输出方程组

输出信号为函数,输入信号和现态为变量

状态转换表(真值表)

现态,输入为变量,次态,输出为结果

米利型和穆尔型分开表示

状态转换图

现态→次态

时序图

CP,A确定后,Q0,Q1,X,Y就确定了

同步时序逻辑电路的分析

一般步骤

做题规范:编号从左到右从高到低,字母从小到大,真值表从小到大排列。(方便阅读)

写逻辑方程组

写出激励方程组

代入触发器的特性方程

组成每个输出变量的输出方程组

根据逻辑方程组,写出状态转换表/图

确定电路的逻辑功能

分析举例

同步时序逻辑电路的设计

一般步骤

由给定的逻辑功能建立原始状态图和原始状态转换表

确定输入变量和输出变量的名称

找出所有可能的状态以及状态转换之间的关系和输入条件

根据原始状态转换图建立原始状态转换表

状态化简

去除多余的状态

状态分配

选择触发器类型

确定激励方程组和输出方程组

画出逻辑图,并检查自校正能力

设计举例

同步时序逻辑电路的时钟偏移

异步时序逻辑电路的分析

常用时序逻辑电路模块

寄存器

每个触发器可以储存一位二进制数,储存N位就用N和触发器

特点

比锁存器有更好的同步和抗干扰性能

移位寄存器

基本移位寄存器

越早输出的信号走的越远

特点

属于同步时序电路

只能用边沿触发

多功能双向移位寄存器

计数器

概念

模

计数周期,在多少个不同的状态下循环

进制

是用几进制表示的(本质还是二进制,例如用四个二进制表示一位十进制数,有两位十进制数,则模数为10²=100)

二进制计数器

异步二进制计数器

特点

分频,可作为分频器使用(第一级就已经是1/2分频了)

时间延迟比较严重,只能工作在低频

同步二进制计数器

递增计数器每个触发器的激励方程

递减计数器

逻辑图

特点

工作速度快

稳定性高

同步计数器的进位

与上图相比,现在每个触发器的输出信号一发生变化,所有与门同时收到,减少传输时间

异步清零和同步并行置数

~CR的优先级最高,为低电平时所有输出置零

~PE具有次优先级,为低电平时时钟触发后输出为预置数

其他模数的计数器

N<M

反馈清零法(异步清零)

如图

特点

出现一个时间很短的不稳定过渡态,可能导致电路故障

反馈置数法(同步置数)

如图

特点

稳定迅速

N>M

异步级联

上一单元的计数器的进位信号作为下一计数器单元的输入

同步级联

基本环形计数器

环形计数器不存在竞争冒险现象

几个触发器就有几个状态

扭环形计数器

状态×2

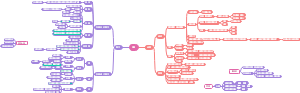

二值逻辑变量与基本逻辑运算

与

或

非

与非

或非

异或

同或

脉冲信号的产生与整形

555定时器及其应用

555定时器

5端一般串小电容接地

用555组成的施密特触发电路

注意同向还是反向

同向

反相取反

反向

正向阙值电压为2/3Vcc,反向阙值电压为1/3Vcc(可通过分压电阻和电源调整)

应用

波形变换(产生方波,脉冲波)(正反馈,波形很陡)

脉冲整形(稳定性,减小噪声和失真)

脉冲鉴幅

用555组成单稳态电路

电路

波形图

应用

定时和延时

555组成的多谐振荡电路

时基集成电路的结构和工作原理

半导体储存器及可编程逻辑器件

储存器

只读存储器(ROM)

非易失

概念

储存容量

字数乘字长(一个数据中所含的位数)

结构图

固定ROM

可编程ROM

可编程只读存储器(PROM)

光可擦可编程只读存储器(UVEPROM)

大电压编程,光擦除

电可擦可编程只读存储器(EEPROM)

快闪存储器(Flash)

全擦除

ROM特点

随时读出,不可随时写入

数据不易丢失,断电也保存

结构简单,集成度高,价格便宜

随机存储器(RAM)

易失

静态随机存储器(SRAM)

静态触发器

动态随机存储器(DRAM)

栅极电容

特点

随时写出,随时写入

读写方便

数据易失,断电就丢失

存储容量的拓展

位拓展(输出长度变长)

适用情况

每片储存器的字数够用而位数不够用时

直接并

字拓展(储存数量变多)

适用情况

位数够用而字数不够用

用储存器实现组合逻辑电路

用真值表

可编程逻辑器件PLD

简单可编程逻辑器件SPLD

基本结构

表示方法

×为可编程点,实心点为固定点

可编程逻辑阵列PLA

可编程阵列逻辑PAL

通用阵列逻辑

复杂可编程逻辑器件CPLD

基本结构

现场可编程门阵列FPGA