导图社区 计算机组成原理(第3版)

- 819

- 27

- 3

- 举报

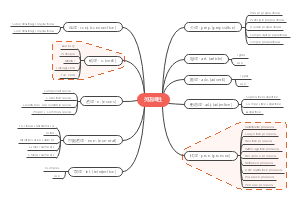

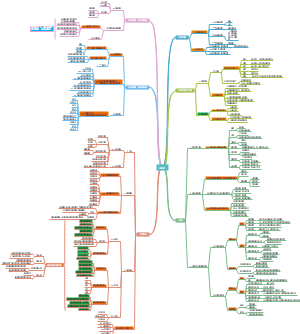

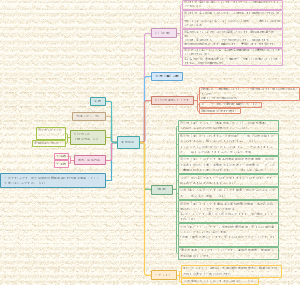

计算机组成原理(第3版)

该本思维导图介绍了计算机的基本组成原理和内部工作机制。共分8章,主要内容分成两个部分:第1、2章介绍了计算机的基础知识;第3-8章介绍了计算机的各子系统(包括运算器、存储器、控制器、外部设备和输入输出子系统等)的基本组成原理、设计方法、相互关系以及各子系统互相连接构成整机系统的技术。喜欢的小伙伴可以点个赞哦!

编辑于2019-08-18 17:11:18- 相似推荐

- 大纲

计算机组成原理(第3版)

1 计算机硬件系统组成的基本概念

1. 理解计算机体系统的层次结构

2. 掌握计算机硬件系统的组成、冯诺依曼计算机的要素和“存储程序”工作原理

3. 了解信息的数字化表示所需的主要步骤和优点

4. 了解计算机系统的主要性能指标

2 计算机中的信息表示

1. 熟练掌握进位计数制、机器数以及定点和浮点表示法

2. 掌握指令格式及可扩展操作码指令系统设计方法

3. 熟练掌握常见寻址方式并能够正确计算操作数地址

4. 掌握外设端口编址方式

5. 了解常见指令类型

6. 理解RISC和CISC两种指令集的各自特点

7. 运算方法

定点运算

定点加减运算

[X+Y]补=[X]补+[Y]补

[X-Y]补=[X]补+[-Y]补

补码加减运算规则

1.参与运算的操作数用补码表示,符号位参与运算,所得结果即为补码形式

2.若操作码为加,则两数补码相加

3.若操作码为减,则将减数变补后再与被减数的补码相加

溢出判断与移位

溢出判断方法

溢出判断一

V=SA'SB'Sf'+SASBSf'

两正数相加,即SA=SB=0,若和为负数,即Sf=1,则V=1产生正溢出

两负数相加,即SA=SB=1,若和为正数,即Sf=0,则V=1产生负溢出

溢出判断二

V=Cf⊕C

当Cf与C不同时,V=1表明有溢出,相同时V=0无溢出

溢出判断三

V=Sf1⊕Sf2

操作数和结果用双符号位,其含义

00-结果为正

01-结果正溢

10-结果负溢

11-结果为负

如果将第一符号位和第二符号位分别定义为Sf1和Sf2,则两个符号位不一致时表明有溢出。但不管结果是否有溢出,第一符号位Sf1将始终指示结果的正负性质。

若Sf1=Sf2,则V=0无溢出;若Sf1≠Sf2,则V=1有溢出。

注:A,B为两个数,用SA、SB分别表示两数的数符,用Sf表示结果的符号,用Cf表示符号位产生的进位,用C表示最高有效数值位(即符号位右边的那位)产生的进位,V=1表示溢出,V=0表示无溢出。

移位操作

逻辑移位

循环左移

循环右移

非循环左移

非循环右移

算数移位

1.正数补码(包括原码)移位规则:数符不变,空位补0

2.负数补码移位规则:数符不变,左移时空位补0,右移时空位补1

舍入处理

1.0舍1入

规则:若第n+1位是0,则舍去后并不作修正;若第n+1位是1,则舍去后第n位加1

2.末位恒置1

规则:不管第n+1位是1还是0,舍去后将第n为恒置为1

定点乘法运算

1.原码一位乘

算法原理[每次将1位乘数所对应的部分积与原部分积的累加和相加,并移位]

2.补码一位乘

3.原码两位乘

定点除法运算

1.原码不恢复余数除法

2.补码不恢复余数除法

浮点运算

浮点加减运算

1.检测能否简化操作

判断操作数是否为0

2.对阶

以大的阶码为基准,调整小的阶码,使两数的小数点位置对齐

3.尾数相加/减

将对阶后的两尾数按定点加/减运算规则求和或者求差

4.结果规格化

为增加有效数字的位数,提高运算精度,必须将求和或者求差的尾数规格化

左规

如果两同号数相加,尾数有进位到符号位,使|M|>=1,则需将尾数右移一位使之规格化

如:00.0101左移00.1010

如:11.1001左移11.0110

尾数左规阶码减少,可能发生下溢

右规

如果两异号数相加(或者同号数相减),使|M|<1/2,则需将尾数左移一位使之规格化

尾数右规阶码增加,可能是上溢

5.舍入

为提高精度,要考虑尾数右移时丢失的数值位

“0舍1入”法

“恒置1”法

6.判断是否溢出

如果阶码采用补码表示,溢出就可以使用双符号位判断溢出的方式来判断此浮点数是否溢出

IF 阶符==01 :上溢,需做中断处理

ELSE IF 阶符==10:下溢,按机器零处理

ELSE :结果正确

浮点乘法运算

1.检测能否简化操作,并置结果数符

2.阶码相加

3.尾数相乘

4.乘积规格化

浮点除法运算

1.检测能否简化操作,并置商的数符

2.尾数调整

3.阶码相减

4.尾数相除

5.结果不再规格化

尾数调整后已规格化

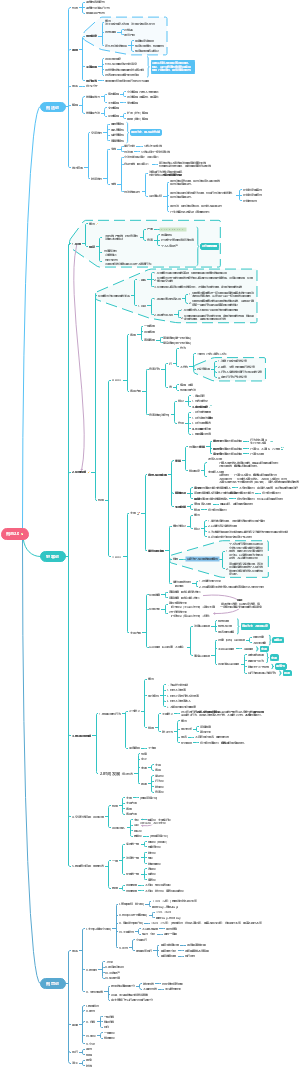

3 CPU子系统

1. 概述

1. CPU的基本组成

1. 运算部件

输入逻辑

算术逻辑运算部件ALU

输出逻辑

2. 寄存器组

通用寄存器组

暂存器

指令寄存器IR

程序计数器PC

程序状态字寄存器PSW

地址寄存器MAR

数据缓冲寄存器MBR

连接CPU与主存的桥梁

3. 控制器及控制方式

4. 时序系统

5. CPU内部的数据通路结构

(1)单组内总线、分立寄存器结构

(2)单组内总线、集成寄存器结构

(3)多组内总线结构

2. CPU的工作原理

1. CPU的主要功能

1.处理指令

2.执行操作

3.控制时间

4.处理数据

2. CPU外部连接

1.北桥芯片组连接

2.PCH芯片组连接

3. CPU控制信息传送方式

1.直接程序传输方式

2.程序中断方式

3.DMA传输方式

4.IOP方式(如通道)

3. CPU的指令集类型

1.复杂指令集计算机CISC

2.精简指令集计算机RISC

2. 指令系统

1. 指令格式

1. 指令中的基本信息

2. 指令中的地址结构

三地址指令

二地址指令

一地址指令

零地址指令

2. 寻址方式

1. 立即寻址

由指令直接给出操作数,在取出指令的同时就取出了可以立即使用的操作数,这样的数被称为立即数(常数),这种寻址方式称为立即数寻址

2. 直接寻址

在指令中直接给出操作数的有效地址,根据有效地址可从主存储器中读取或写入操作数,这种方式称为直接寻址

3. 寄存器直接寻址(寄存器寻址)

在指令中直接给出寄存器号,操作数实际存储在指定编号的寄存器中

4. 主存间接寻址

指令中给出主存间址单元地址(间接地址,操作数地址的地址),按照该地址访问主存中的间址单元,从中读取操作数地址,按操作数地址再次访问主存,然后从相应单元读取或写入操作数。

5. 寄存器间接寻址

在指令中给出寄存器号,指定的寄存器中存放的是操作数的有效地址,按照该有效地址访问主存,读取或写入操作数

变型

1.自增型寄存器间址

先操作,再操作数地址加1

2.自减型寄存器间址

先操作数地址减1,再操作

6. 变址寻址

指令中分别给出一个寄存器和一个形式地址,寄存器中的内容作为偏移量,形式地址作为基准地址,将基准地址和偏移量相加得到操作数的有效地址,再按此地址访问主存,从相应的主存单元中读取操作数,或把操作数写入此主存单元。

有效地址=形式地址+变址量

7. 基址寻址

指令中分别给出一个寄存器号和一个形式地址,寄存器中的内容作为基准地址,形式地址作为偏移量,将基准地址与偏移量相加作为操作数的有效地址,再按此地址访问主存,在相应的主存单元中读取或写入数据

基址寻址方式和变址寻址方式异同

1.基址寻址方式和变址寻址方式的有效地址计算法几乎一样,差别在于:变址寻址中形式地址给出的是基准地址,寄存器给出的是偏移量;基址寻址中的形式地址给出的是偏移量,而寄存器给出的是基准地址。

2.两种寻址方式的具体应用也不同:变址寻址方式立足于面向用户,可用于访问字符串、数组、表格等成批数据(或其中的某些元素);基址寻址方式立足于面向系统,可用来解决程序在实际主存中的重定位问题,以及在有限字长指令中扩大寻址空间等。

8. 基址加变址寻址

指令中给出一个基址寄存器号RB、一个变址寄存器号RX和一个形式地址D,基址寄存器的内容作为基准地址,变址寄存器的内容作为变址偏移量,形式地址作为常规偏移量。

操作数的有效地址=基准地址+变址偏移量+常规偏移量

9. 相对寻址

将程序计数器PC当前的内容作为基准地址,指令中给出的形式地址为偏移量(可正、可负),两者相加后形成操作数的有效地址

若取指时PC的内容为A,按地址A从主存中读取指令放入IR,然后PC的内容自动加1。指令中的形式地址字段给了偏移量d,它表示从当前PC值(即A+1)到操作数所在单元之间的距离。

操作数的有效地址=A+1+d

10. 页面寻址

PC的高位段作为高位段,指令给出的形式地址d作为低位段,操作数的有效地址由这两部分地址段拼接而成

操作数有效地址=(PC)H∪d

11. 堆栈寻址

堆栈寻址方式是专门用于访问堆栈的寻址方式,操作数在堆栈中,指令隐含约定由堆栈指针SP寄存器提供栈顶单元地址,进行读出或写入。

3. 指令的功能和类型

1.传输类指令

1.传输指令:实现CPU中各寄存器之间的数据传送

2.访存指令:实现对存储器的读出或写入

3.I/O指令:将有关I/O接口中寄存器的内容输入到主机(CPU的寄存器中或主存储器中)或是将数据从主机输出到I/O接口中

2.访存指令

1.加载指令(读存储器)

2.存储指令(写入存储器)

3.弹出(POP)

4.压栈(PUSH)

3.输入/输出(I/O)指令

I/O指令所传输的信息分为

数据

命令

状态

(1)I/O设备的编址方法

1.外围设备单独编址

2.外围设备与主存储器统一编址

(2)I/O指令的设置方法

1.设置专用的I/O指令

2.采用通用的数据传输指令实现I/O操作

4.算术逻辑运算指令

(1)算术运算指令

加(ADD)

减(SUB)

加1(INC)

减1(DEC)

求补(NEG)

(2)逻辑运算指令

与(AND)

或(OR)

非(COM)

异或(EOR)

(3)移位指令

1.算术移位指令

2.逻辑移位指令

(4)串操作指令

(5)专用的数据处理指令

转换指令

检索指令

编辑指令

5.程序控制类指令

(1)转移指令

1.无条件转移指令

2.条件转移指令

有进位转移JC

无进位转移JNC

有溢出转移JO

无溢出转移JNO

为零转移JZ

不为零转移JNZ

为正转移JNS

为负转移JS

(2)转子程序指令与返回指令

1.转子程序指令

2.返回指令

(3)软中断(程序自中断)指令

区别:软中断的操作与转子程序很相似,不同之处是,这种软中断指令可以随机地插入到程序的任何位置

(4)控制处理机某些功能的指令

(5)面向操作系统的一些指令

1.访问系统寄存器的指令

2.检查保护属性的指令

3.用于存储管理的指令

3. CPU的基本模型

1.CPU设计步骤

2.模型机的指令系统

1.指令格式

2.寻址方式

寄存器寻址 R

寄存器间接寻址 (R)

自减型寄存器间址

-(R)

-(SP)

立即/自增型寄存器间址

(R)+

(SP)+

(PC)+

直接/自增型双重间址

@(R)+

@(PC)+

变址/相对寻址

X(R)

X(PC)

跳步 SKP

3.指令类型

3.模型机的组成与数据通路

1.部件设置

2.总线与数据通路结构

1.内总线

2.系统总线

地址总线

数据总线

控制总线

3.各类信息的传输路径

1.指令信息的传输

2.地址信息的传输

3.数据信息的传输

记住微指令操作过程

4. 运算部件

5. 组合逻辑控制方式

1.组合逻辑控制器时序系统

1.工作周期(机器周期)

1.取指周期FT

2.源周期ST

3.目的周期DT

4.执行周期ET

5.中断周期IT

6.DMA周期DMAT

2.时钟周期(节拍)

3.工作脉冲

2.指令流程与操作时间表

CPU执行指令的工作机制

1.在寄存器传输级

2.拟定操作时间表

1.取指令周期FT

2.MOV指令

3.双操作数指令

4.单操作数指令

5.转移指令JMP/返回指令RST

6.转子指令JSR

7.中断周期IT

3.微命令的综合与产生

4.优缺点

6. 微程序控制方式

1.微程序控制的基本原理

1.基本思想

2.逻辑组成

3.工作过程

2.微指令编码与微地址形成

1.微指令的编码方式

(1)直接控制法(不译法)

(2)分段直接编译法(显式编码、单重定义)

(3)分段间接编译法(隐式编码、多重定义)

(4)其他编译方法

1.微指令译码与机器指令译码复合控制

2.微地址参与解释微指令代码

2.微地址的形成方式

(1)初始微地址的形成

1.取机器指令

2.功能转移

一级转移

多级转移

采用PLA电路实现功能转移

(2)后继微地址的形成

1.增量方式(顺序执行-转移方式)

2.断定方式

3.优缺点

7. CPU性能的提升方式

1.流水线技术

1.流水线的常见种类

(1)按流水线的处理层级

1.功能部件级

2.指令级

3.处理器级

(2)按完成的功能数量

1.单功能流水线

2.多功能流水线

(3)按处理的数据形态

1.标量流水线

2.向量流水线

(4)按流水线部件的连接模式

1.线性流水线

2.非线性流水线

(5)按输入输出顺序的一致性

1.顺序流水线

2.乱序流水线

2.流水线的性能指标

1.吞吐量

2.加速比

3.使用效率

3.标量和超标量流水线

4.超级流水线

5.超标量超流水线技术

6.与流水线相关的其他技术

(1)超长指令字

(2)向量机

(3)SIMD技术(单指令多数据)

2.SMT与超线程

3.多核技术

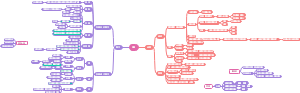

4 存储子系统

1. 概述

1. 存储系统的层次结构

1.1. 主存储器

1.2. 外存储器(辅助存储器、后援存储器)

1.3. 高速缓冲存储器

Cache访问命中

静态随机访问存储器(SRAM)

2. 物理存储器与虚拟存储器

3. 存储器的分类

3.1. 物理存储机制(存储介质)

(1)半导体存储器

1.静态存储器

2.动态存储器

(2)磁表面存储器

(3)光盘存储器

3.2. 存储方式

(1)随机访问存储器RAM

(2)顺序访问存储器SAM

(3)直接访问存储器DAM

3.3. 读写特性

可读可写型存储器RWM

只读存储器ROM

3.4. 存储器在系统中的位置

主存储器

外存储器

高速缓冲存储器

4. 存储器的技术指标

1. 存取时间

2. 存取周期

3. 数据传输率

2. 半导体存储原理

2.1. 双极型存储单元

SN74189

2.2. 静态MOS存储单元

Intel 2114

2.3. 动态MOS存储单元

原理:将存储信息以电荷形式存于电容之中,这种电容可以是MOS管栅极电容或者专用的MOS电容,通常将其定义为电容充电至高电平,对应得信息位1;放电至低电平,则对应的信息为0

Intel 2164

41128

2.4. 半导体只读存储器

(1)掩膜型只读存储器MROM

(2)可编程序(一次编程型)只读存储器PROM

(3)可擦除重编程只读存储器EPROM

Intel 2716

(4)电可擦除重编程只读存储器EEPROM

(5)新一代可编程只读存储器FLASH

3. 主存储器的组织

3.1. 主存的设计原则

(1)驱动能力

(2)存储器芯片类型选择

(3)存储器芯片与CPU的时序配合

(4)存储器的地址分配和片选译码

(5)行选信号RSA'和列选择信号CAS'的产生

3.2. 主存的逻辑设计

位扩展

编址空间的扩展

存储器逻辑设计的方法步骤

1.存储空间分配与芯片选择

2.地址分配与片选逻辑

3.存储器设计方案的逻辑结构图

线选法

译码片选法

3.3. 主存的外部连接方式

(1)系统的结构模式

1.最小系统模式

2.较大系统模式

3.专用存储总线模式

(2)速度匹配与时序控制

(3)数据通路匹配

(4)有关主存的控制信号

3.4. 常见的主存芯片技术

(1)同步突发静态随机存储器SB SRAM

(2)多端口静态随机存储器MP SRAM

(3)先进先出存储器FIFO SRAM

(4)扩展数据输出动态随机存储器EDODRAM

(5)同步动态随机存储器SDRAM

(6)双数据率同步动态随机存储器DDR SDRAM

3.5. 存储器的刷新与校验

1.动态随机存储器的刷新

1.集中刷新方式

2.分散式刷新方式

3.异步刷新方式

2.主存储器的校验

1.奇偶校验

2.ECC校验

4. 磁表面存储原理

4.1. 存储介质与磁头

4.2. 读写原理

1.水平磁化方式

2.垂直磁化方式

4.3. 磁记录的编码方式

1.不归零-1制(NRZ1)

规律:见1则翻转

2.调相制(PM)

规律:1、写0,在单元中间位置让写入电流负跳变,由+I→-I

2、写1,在单元中间位置让写入电流正跳变,由-I→-I

3、若相邻位相同,则两位交界处写入电流需改变一次方向,才能使相同两位的磁化翻转相位一致;若相邻两位不同,交界处没有翻转。

3.调频制(FM)

规律:1、每个位单元起始处写入电流都改变一次方向

2、如果写入0,则位单元中间不变;如果写入1,则写入电流在位单位中间改变一次方向

4.改进型调频制(MFM或M²F)

规律:1、每个位单元起始处写入电流都改变一次方向

2、写1时,在位单元中间改变写入电流方向

3、写入两个以上0时,在它们的交界处改变写入电流方向

5.群码制(GCR)

5. 磁盘存储器及其接口

5.1. 软盘存储器

5.2. 硬盘存储器

1.盘片、盘组、磁盘阵列

2.温彻斯特技术

3.磁头定位系统

开环控制

闭环控制(反馈)

4.硬盘信息分布与寻址信息

1.磁道

2.圆柱面

3.数据块

5.磁道记录格式

6.硬盘存储器的发展方向

5.3. 技术指标与数据校验

1.磁盘格式化

2.磁盘存储器技术指标

(1)磁盘容量

1.非格式化容量:面数×道数/面×内圈周长×最大位密度

2.格式化容量:面数×道数/面×扇区数/道×字节数/扇区

(2)工作速度

1.平均寻道(定位)时间

2.平均旋转延迟(等待)时间

3.数据传输率(带宽)

3.磁盘的数据校验

海明校验

循环冗余校验

5.4. 磁盘适配器

6. 存储系统性能的改进措施

6.1. 高速缓冲存储器

1.地址映射方式

(1)直接映射

(2)全相联映射

(3)组相联映射

2.常用的替换算法

(1)先进先出算法(FIFO)

(2)近期最少使用算法(LRU)

3.Cache的读写过程

(1)读操作

(2)写操作

“回写”法

“通写”法

“一次写”法

6.2. 虚拟存储器

1.页式虚拟存储器

2.段式虚拟存储器

3.段页式虚拟存储器

6.3. 双端口存储器

6.4. 并行存储器

1.单体多字并行主存系统

2.多体交叉存取方式的并行主存系统

3.并行处理机与多机系统中的存储组织

6.5. 联想存储器

5 总线与输入/输出子系统

1. 概述

1. 总线简介

2. 接口的功能与类型

1. I/O接口的基本功能

(1)寻址

(2)数据传输与缓冲

(3)数据格式变换、电平变换等预处理

(4)控制逻辑

2. I/O接口的编址

1.外设独立编址

2.外设与主存统一编址

3. I/O接口分类

(1)按数据的传输格式分类

1.并行接口

2.串行接口

(2)按时序控制方式分类

1.同步接口

2.异步接口

(3)按信息传输的控制方式分类

1.直接程序传输方式接口

2.中断接口

3.DMA接口

3. 输入/输出控制方式

1. 直接程序传输方式

2. 中断方式

3. DMA方式

4. IOP和PPU方式

2. 总线

分为单总线结构和多总线结构

定义

1. 总线的特性与分类

1.1. 总线的特性

1.物理特性

2.功能特性

3.电气特性

4.时间特性

1.2. 总线的分类

(1)从功能分类

数据总线

控制总线

地址总线

(2)按数据传输格式分类

并行总线

串行总线

(3)按时序控制方式分类

同步总线

异步总线

(4)按总线的结构层次分类

芯片内总线

局部总线

系统总线

外部总线

2. 总线的标准

ISA总线、EISA总线、AGP总线、PCI和PCI-EXpress

1. 机械结构规范

2. 功能规范

3. 电气规范

3. 总线的设计要素

3.1. 总线的技术指标

(1)总线宽度

(2)总线频率

(3)总线带宽与数据传输率

3.2. 总线周期与操作过程

总线周期

指CPU完成一次访问主存或I/O端口操作所需的时间

总线操作步骤

1.主设备申请总线控制权

2.主设备掌握总线控制权

3.从设备响应,主-从设备之间进行数据传输

4.主设备释放控制权,结束总线周期

总线上的数据传输模式

1.单周期模式

2.突发模式

3.3. 总线的控制方式

(1)同步控制方式

(2)异步控制方式

1.不互锁

2.半互锁

3.全互锁

3.4. 总线的仲裁

(1)集中式总线仲裁

1.链式查询方式

2.计数器定时查询方式

3.独立请求方式

(2)分布式总线仲裁

4. PCI总线介绍

4.1. 信号组成

4.2. 总线仲裁

PCI总线使用的是集中式总线仲裁器,独立请求方式

3. 直接程序传输方式与接口

1. 概念:

数据在CPU和I/O设备间直接交换,CPU执行程序来直接控制I/O操作,程序中由一系列的检测设备状态、发送读或写命令以及数据传输的指令组成。在这种方式中,当CPU发送一个命令后,它必须等待,直到外设操作完成。

2. 优缺点:

硬件开销小,实时处理能力差,并行程度低,CPU大部分时间处于等待状态,利用率低

4. 中断方式与接口

1. 中断的相关概念

1.1. 定义

在计算机的运行过程中,如果发生某种随机事态,CPU将暂时执行现行程序,转去执行中断处理程序,为该随机事态服务,并在服务完毕后自动恢复原程序的执行

特点:程序切换性和随机性

中断与子程序两者的本质区别:P297

1.2. 中断方式的典型应用

1.以中断方式管理中低I/O操作,使CPU与外部设备并行工作

2.软中断

3.故障处理

4.实时处理

5.多机通信

6.人机对话

1.3. 中断系统的硬件、软件组织

1.4. 中断的分类

1.硬件中断和软件中断

2.强迫中断与自愿中断

3.内中断与外中断

4.可屏蔽中断与非屏蔽中断

5.向量中断和非向量中断

2. 中断请求

2.1. 中断请求逻辑

2.2. 中断请求信号的传输

3. 中断判优

3.1. CPU与中断请求之间的判优

3.2. 中断请求之间的判优

(1)软件查询

(2)并行优先级排队逻辑

(3)链式优先排队逻辑

(4)二维结构的优先排队

(5)采用中断控制器集成芯片的优先逻辑

4. 中断响应

4.1. 中断服务程序入口地址的获取方式

(1)向量中断方式

1.中断向量

2.中断向量表

3.向量地址

(2)非向量中断方式

4.2. 响应中断的条件

1.有中断请求信号发生

2.该中断请求未被屏蔽

3.CPU处于开中断状态,即中断允许触发器(或中断允许标志位)为1

4.没有更重要的事件要处理

5.CPU刚刚执行的指令不是停机指令

6.在一条指令结束时响应

4.3. 中断响应过程

1.关中断

2.保护断点

3.获取服务程序的入口

4.转向程序运行状态

5. 中断处理

5.1. 现场保护

5.2. 多重中断与单级中断

5.3. 恢复现场、返回到原程序

6. 中断接口组成模型

7. 典型中断接口举例

5. DMA方式与接口

1. DMA方式基本概念

1.1. 定义

DMA即直接存储器访问,依靠硬件直接在主存与外围设备之间进行数据传输,在传输过程中不需要CPU的干预

1.2. 特点与应用

与程序中断方式的比较P319

1.3. 单字传输方式与成组传输方式

1.4. 硬件组织

1.5. 程序准备(DMA初始化)

2. DMA控制器与接口的连接

2.1. 单通道型DMA控制器

2.2. 选择型DMA控制器

2.3. 多路型DMA控制器

2.4. 多个DMA控制器的连接

3. DMA控制器的组成

4. DMA传输操作过程

4.1. 预处理

4.2. 数据传输

4.3. 后处理

5. 典型DMA接口举例

6. IOP和PPU

1. 通道的系统结构

2. 通道的类型

3. 通道的工作原理