导图社区 信号完整性

- 653

- 37

- 8

- 举报

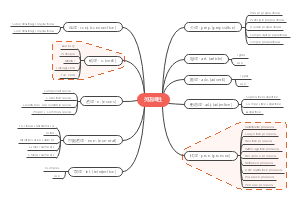

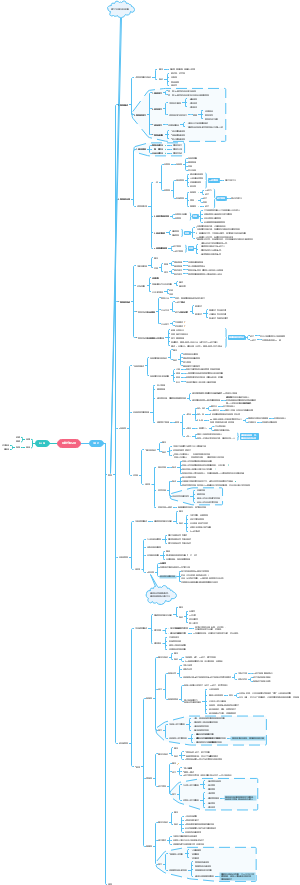

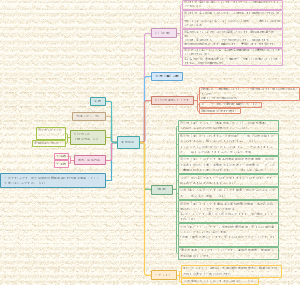

信号完整性

信号完整性基础知识点归纳总结思维导图

编辑于2018-12-28 08:10:25- 完整性

- 相似推荐

- 大纲

信号完整性

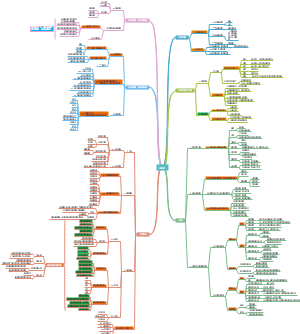

数字信号的频谱和带宽

傅里叶变换

时域信号可以看作由很多频谱分量叠加而成的,典型的理想方波信号

信号上升时间与带宽的关系

信号上升时间越小,带宽越大,包含的高频分量越多

带宽

BW=0.35/Tr,Tr指的是10%~90%的信号上升时间

总结

高速时代,数字信号的边沿十分陡峭,信号中含有极高的频率成分,这些高频成分是导致信号完整性的根源。

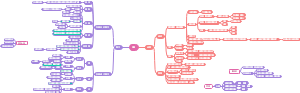

传输线理论

什么是传输线

为电磁波向前传输提供物理环境

信号的传播速度

6000mil/ns=6inch/ns

传输线返回电流

使用传输线理论理解返回电流的产生,使用“动态思维”

单位长度电容

单位长度电感

电报方程

为理解信号反射,传输线特性阻抗,传输线延时提供了理论基础

瞬态阻抗与特性阻抗,Z=√L/C

如果传输线均匀则为特性阻抗

影响特性阻抗的因素

线宽

线宽越宽,特性阻抗越小

介质厚度

介质厚度越大,特性阻抗越大

介电常数

介电常数越大,特性阻抗越小

走线的铜箔厚度

走线的铜箔厚度越大,阻抗越小

如果传输线不均匀则为瞬态阻抗

参考平面

提供返回电流路径

阻抗控制功能

返回电流的分布

返回电流大部分从参考平面返回,走线两侧的铜皮占很小一部分,若进一步加大走线间距,则承载的返回电流更小

传输线形式

微带线

PCB表层走线

带状线

PCB内层走线

同轴线

双绞线

理想传输线的集总参数模型

耦合传输线模态分析

静态

信号处于静止状态

奇模工作状态

两条线上的信号反向跳变

偶模工作状态

两条线上的信号同向跳变

模态对阻抗的影响

奇模阻抗,Zodd

奇模状态时,电感减小,电容增大,阻抗减小

偶模阻抗,Zeven

偶模状态时,电感增加,电容不变,阻抗增大

特别强调,奇模阻抗,偶模阻抗指的是一条信号线上的阻抗

线间距对耦合传输线阻抗的影响

表层微带线

内层带状线

有损传输线

阻抗损耗

介质损耗

耦合到临近线

阻抗不连续

对外辐射

趋肤效应

邻近效应

有损传输线的集总参数模型,RLGC模型

传输线的延时

信号的反射

反射的形成

传输线阻抗发生变化

传输线线宽的变化

传输线通过过孔,布线层的变化

参考平面的变化

通过连接器,连接多个PCB网络

传输线上分支结构和引入芯片的Stub线

终端负载的阻抗与传输线阻抗不一致

反射系数Γ=(Z2-Z1)/(Z2+Z1)

末端开路Z2无穷大,反射系数为1

末端短路Z2等于0,反射系数为-1

传输系数T=(2*Z2)/(Z2+Z1)

正反射和负反射

当发生反射时,反射的是信号的波形,而不是电压值

容性阻抗不连续

与电阻性阻抗不连续不同的是,容性阻抗不连续点的阻抗随时间在变化,所以反射系数也在变化

互连线末端容性负载的反射

典型事例:焊盘,封装会存在寄生电容

影响

发送端波形上升沿会出现回沟

延长接收端信号的上升时间

影响因素

容性负载越大,反射噪声越大

信号上升时间越短,反射噪声越大

互连线中间容性负载的反射

典型事例:PCB走线过孔换层,菊花链结构,Fly-By结构

影响(对于接收端)

信号的上升沿变缓

高电平和低电平都会叠加一定的噪声

影响因素

容性负载越大,反射噪声越大

信号上升时间越短,反射噪声越大

感性阻抗不连续

对于感性不连续点,阻抗随时间变化,反射系数也随之变化

互连线末端感性负载的反射

互连线中间感性负载的反射

残桩与分支

分支越短,对信号的影响越小

临界长度

传输线末端信号能否达到振铃最大幅度的传输线长度的临界值

阻尼电阻

菊花链拓扑结构中,在每个分支上串联一个小电阻

反射的预防

仔细设计系统的层叠结构,按照阻抗一致的设计原则,来决定各个布线层传输线的物理几何参数,以达到期望的阻抗值

仔细设计信号的回流路径,保证回流路径的完整性,能够为传输线提供一致的参考平面

按照阻抗匹配的设计原则,放置匹配电阻来控制反射的发生以及吸收发射能量

仔细设计传输路径拓扑结构,尽量减少分支数量和Stub线的长度,最大程度减小发射发生的机会和发射能量。

端接

使源阻抗与传输线阻抗匹配

串联端接

不增加额外功耗

普遍适用于源端阻抗匹配

可通过仿真软件来确定阻值大小以及PCB摆放位置

串联端接中的桩线

串联端接电阻的位置越靠近驱动器信号质量越好

使负载阻抗与传输线阻抗匹配

末端并联端接上拉到电源

端接电阻等于传输线阻抗

引入了直流偏移,增加功耗

拉高信号的低电平

可能导致接收端信号无法满足门限电平的要求

末端并联端接下拉到地

端接电阻等于传输线阻抗

引入了直流偏移,增加功耗

拉低信号的高电平

可能导致接收端信号无法满足门限电平的要求

戴维南端接

必须满足端接电阻R1//R2=Z0

引入了直流偏移,但直流工作点可控,增加功耗

根据接收器高低电平噪声容限的不同,可以通过调节上下拉电阻R1和R2的阻值关系,调整接收端信号的中值电平的位置

以电池为电源的手持设备中禁止使用

AC端接

端接电阻R等于传输线的特性阻抗

电容切断了直流通路,消除了直流功耗

不会出现并联端接中高电平被拉低,低电平被抬高的现象

要求链路中传输的是直流平衡信号,例如:时钟信号,不适合突发模式的数据传输

电容值选择的影响因素

传输线延时

信号的游程长度对应的时间

并联端接的位置

并联电阻与接收器之间的桩线越长,接收器信号噪声越大

拓扑结构

点对点拓扑结构

结构简单,阻抗容易控制

适合高速率,双向传输

既可以串联端接也可以并联端接

T型拓扑结构

各个分支等长

适用芯片驱动多个负载且信号单向传输

通常适用源端串联端接

菊花链拓扑结构

分支桩线尽量短

通常采用末端并联端接

Fly-By拓扑结构

菊花链结构的改进形式

桩线几乎为0

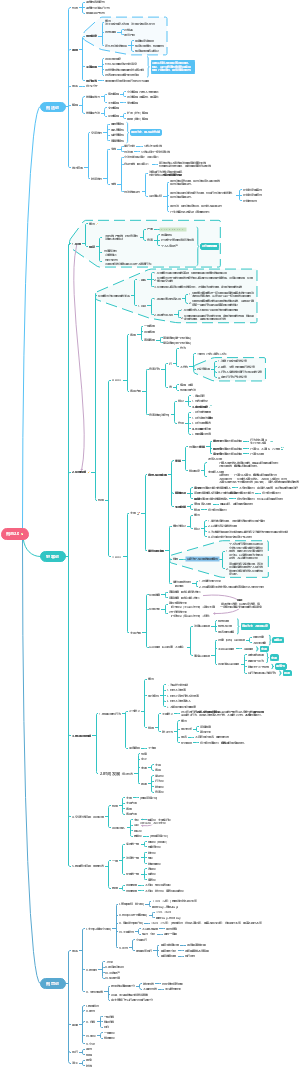

串扰

串扰的根源在于耦合

通过电场发生耦合

容性串扰

通过磁场发生耦合

感性串扰

耦合长度

信号的传播速度V*信号的上升时间Tr

远端串扰

呈现为宽度很窄但幅度很高的窄脉冲

特性

表层走线有远端串扰,内层走线可近似认为没有远端串扰,尽量不要在表层走很长的平行线

远端串扰也会饱和,饱和串扰量为攻击信号幅度的一半

远端串扰的饱和长度一般很大,远大于近端串扰饱和长度

远端串扰饱和长度和信号上升时间、耦合线间距等因素有关

信号上升时间Tr越小,饱和长度越短

线间距越大,饱和长度越长

近端串扰

呈现为幅度不高但时间上展宽的宽脉冲

近端串扰饱和

串扰饱和长度=(信号的上升时间Tr*信号的传播速度Vp)/2

边沿耦合与宽边耦合的串扰

同层走线之间的耦合为边沿耦合

不同层走线之间的耦合为宽边耦合

宽边耦合产生的串扰远远大于边沿耦合的串扰

影响串扰的因素

信号的上升时间

近端串扰未包含时,随信号上升时间减小而增大

通常情况下很难达到远端串扰饱和条件,随信号上升时间减小而增大

介质厚度的影响

对于阻抗控制线,线宽越宽,介质越厚,线间距固定的情况下,串扰越大。

介电常数的影响

介电常数本身不影响串扰大小。但为了控制阻抗,使用小介电常数的板材时,必须要减小层叠厚度,而串扰对层叠厚度很敏感,一次间接减小可串扰。

蛇形走线

尽量使用大的gap值并减小H值,既蛇形走线的突起尽量宽而且矮。

保护地线

表层走线

对于低频模拟信号,保护地线能够起到作用

对于高速数字信号,需要在保护地线上打非常密集的GND过孔

内层走线

保护地线可以减小近端串扰

减小串扰的方法

增大走线间距,采用3W原则

最小化信号线间的平行长度

做好匹配端接。减小串扰噪声的反射

相邻的信号层,走线彼此正交

在内层走线,消除远端串扰

在满足时序的前提下,尽量增大信号的上升时间

个别特殊信号(低频模拟信号)可使用保护地线

高速数字信号谨慎使用保护地线

阻抗控制情况下,使用小介电常数的板材

差分走线

差分传输

差分信号

Vdiff=VP-Vn

共模信号

Vcomm=(Vp+Vn)/2

差分对的返回电流

返回电流主要集中在参考平面,而不是另一条走线

实际工程中,采用差分方式传输的信号往往是非常重要的信号,因此差分对更应该注意参考平面的连续性

阻抗参数

差分阻抗 Zdiff=2Zodd

共模阻抗 Zcomm=Zeven/2

奇模阻抗和偶模阻抗是两条线处于奇模和偶模工作状态下单根传输线的阻抗;差分阻抗和共模阻抗是差分信号和共模信号感受到的阻抗

反射和端接

对差分信号和共模信号同时端接

T型端接

R1=Zodd R2=(Zeven-Zodd)/2

Π型端接

R1=(2ZevenZodd)/(Zeven-Zodd) R2=Zeven

差分互连的串扰

使用差分传输,最有效的减小串扰的方法依然是尽量拉开和攻击信号的间距

差分与共模的相互转化

原因:两个单端信号不可能完全对称,造成信号边沿错位

差分对等长等距

设计时优先保证等长要求

松耦合和紧耦合

工程设计中,对于通道长度很短或信号速率不高的差分互连,可以使用紧耦合以获取更大的布线密度;对于走线很长或信号速率很高的差分互连最好使用松耦合以获得更大的噪声余量

总结

任意两条线都可以传输差分信号,并非一定要有耦合,但适度耦合可带来一定好处

差分对的返回电流位于参考平面上,参考平面对于差分线非常重要

合理的差分设计可以提高抗噪能力

分清差分阻抗、共模阻抗、奇模阻抗、偶模阻抗

差分信号和共模信号会相互转换

共模噪声对差分传输有影响,影响大小和差分对的对称性以及是否有共模端接有关

对称、等长、等距是差分设计的基本要求

使用松耦合还是紧耦合视情况而定,松耦合可以带来性能上的提高